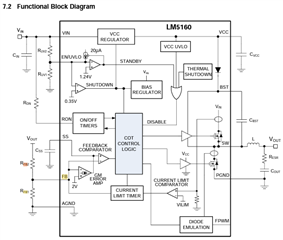

Other Parts Discussed in Thread: LM5160, LM5160A

主题中讨论的其他器件:LM5160、

尊敬的 TI 团队

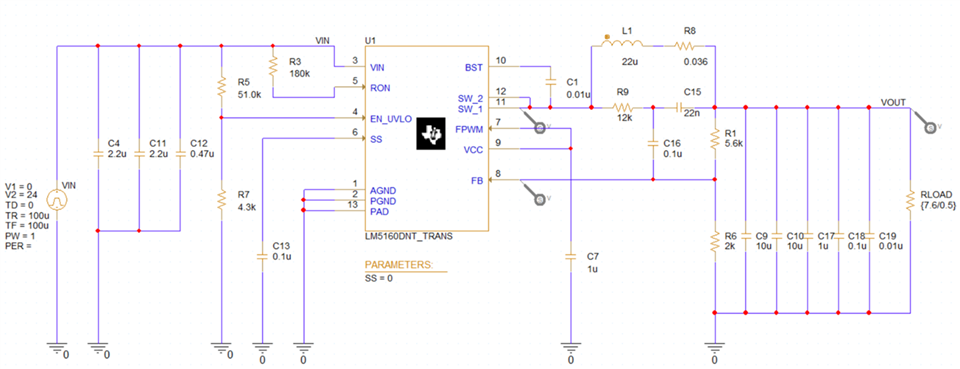

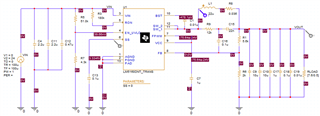

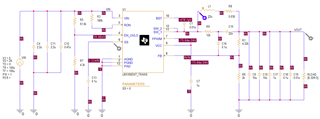

我将在 PSpice 上运行 LM5160的仿真。

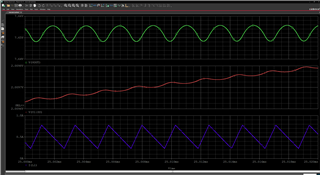

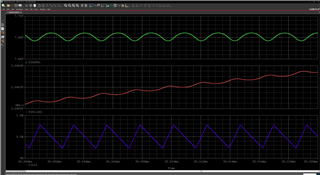

我能够确认、它基本上能够按预期工作。

有一件事让我困扰,我正在与你联系。

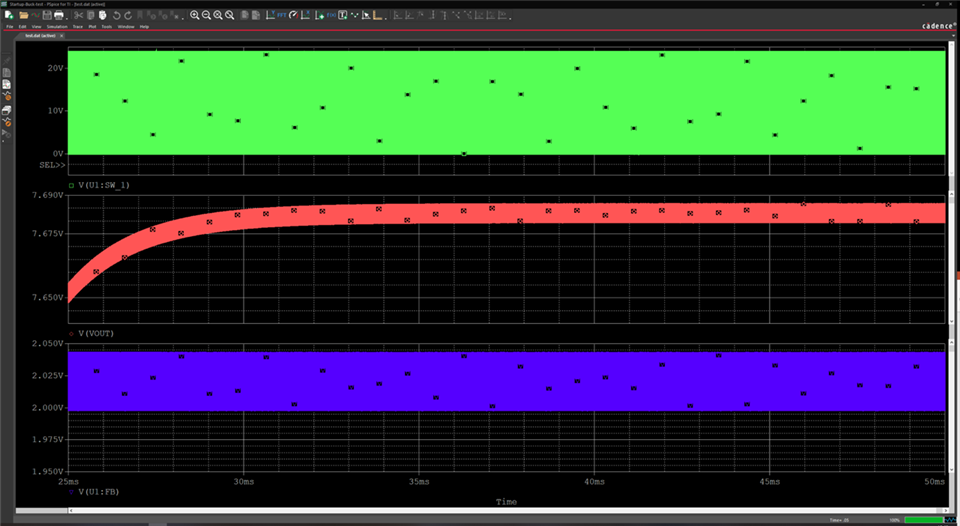

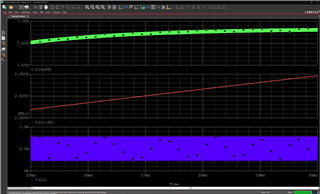

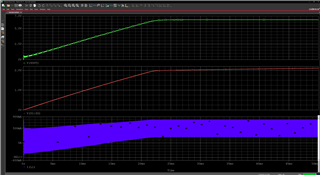

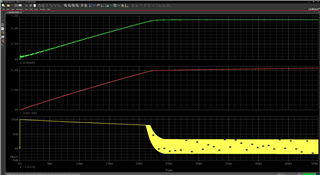

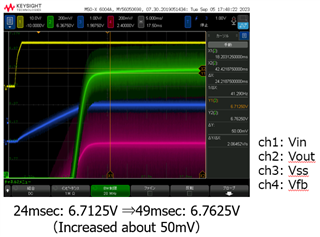

在上电后经过软启动时间后、VFB 的底部电压会稳定为2.0V。

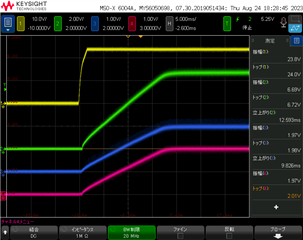

因此、我认为在下面的波形中、VOUT 稳定至少在25ms。

然而、在仿真结果中、电压似乎上升到大约33ms。

如果您对此有任何疑问、敬请告知。

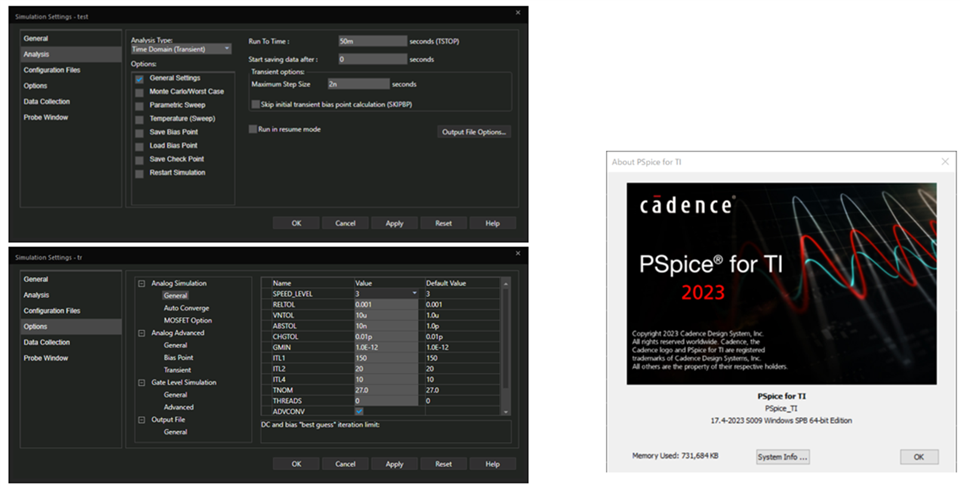

我们还会向您发送仿真设置和工具版本、以备不时之需。

此致、

太郎美