主题中讨论的其他器件:LM5160、

尊敬的 TI 团队

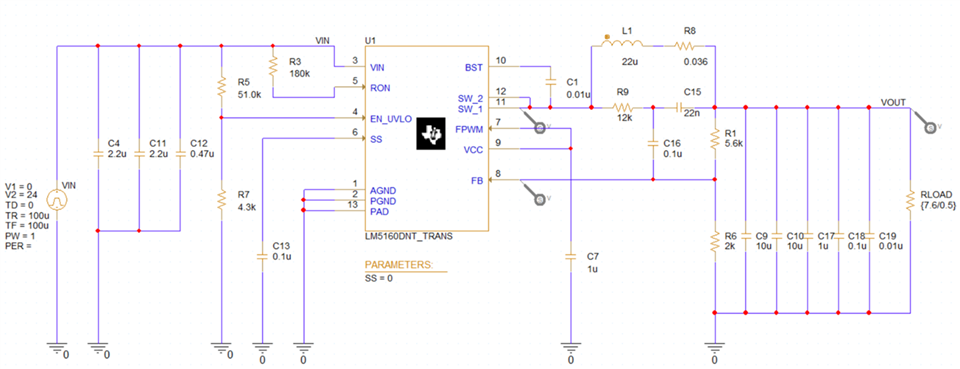

我将在 PSpice 上运行 LM5160的仿真。

我能够确认、它基本上能够按预期工作。

有一件事让我困扰,我正在与你联系。

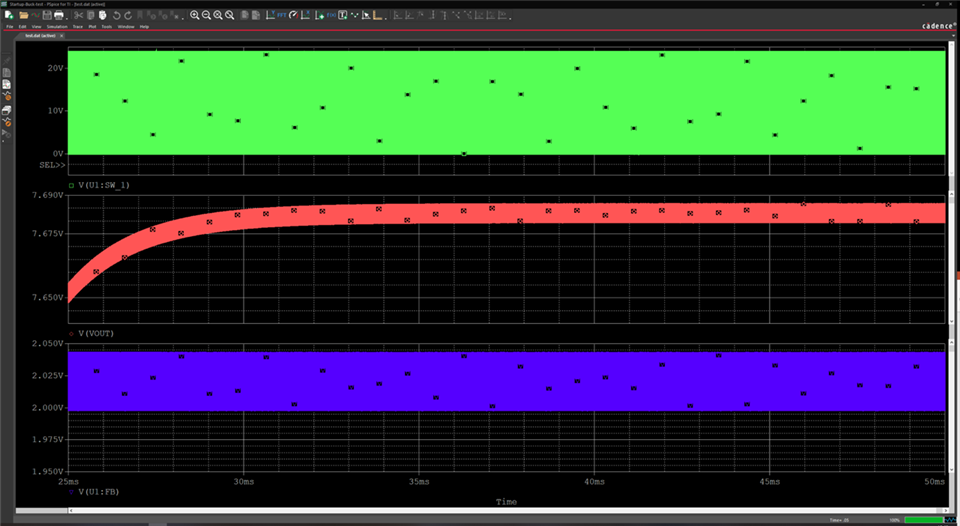

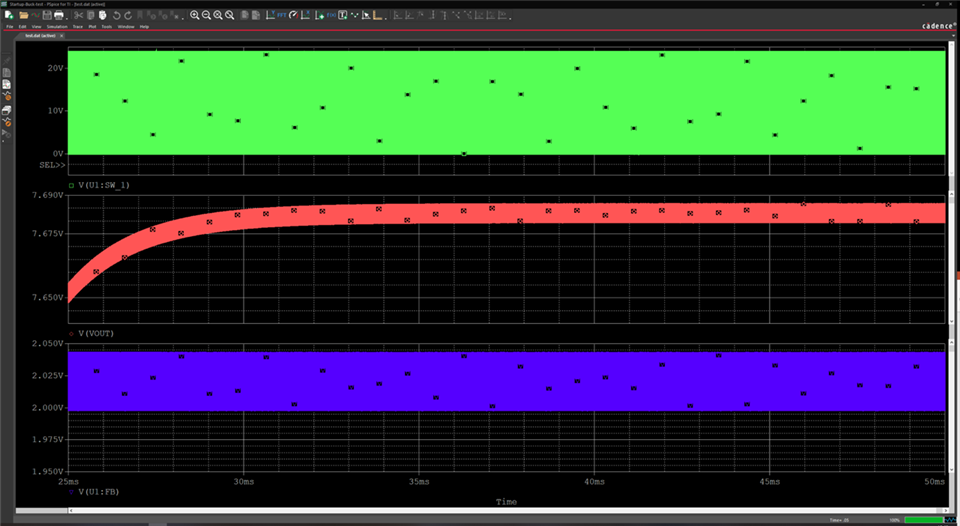

在上电后经过软启动时间后、VFB 的底部电压会稳定为2.0V。

因此、我认为在下面的波形中、VOUT 稳定至少在25ms。

然而、在仿真结果中、电压似乎上升到大约33ms。

如果您对此有任何疑问、敬请告知。

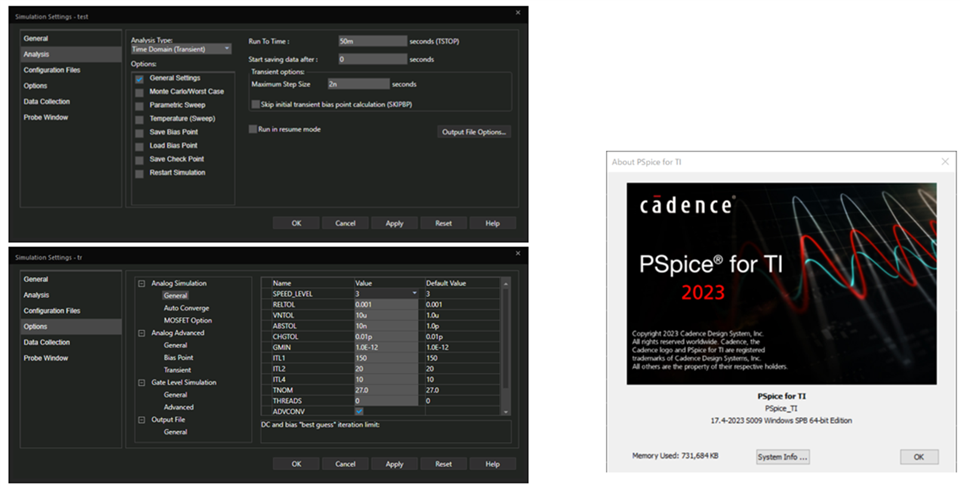

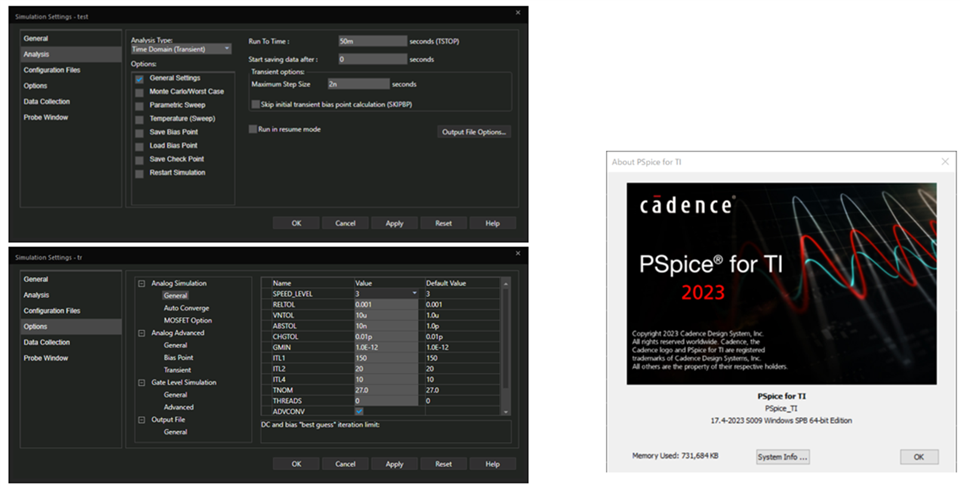

我们还会向您发送仿真设置和工具版本、以备不时之需。

此致、

太郎美

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 TI 团队

我将在 PSpice 上运行 LM5160的仿真。

我能够确认、它基本上能够按预期工作。

有一件事让我困扰,我正在与你联系。

在上电后经过软启动时间后、VFB 的底部电压会稳定为2.0V。

因此、我认为在下面的波形中、VOUT 稳定至少在25ms。

然而、在仿真结果中、电压似乎上升到大约33ms。

如果您对此有任何疑问、敬请告知。

我们还会向您发送仿真设置和工具版本、以备不时之需。

此致、

太郎美

您好、您好。

感谢您提供的信息、

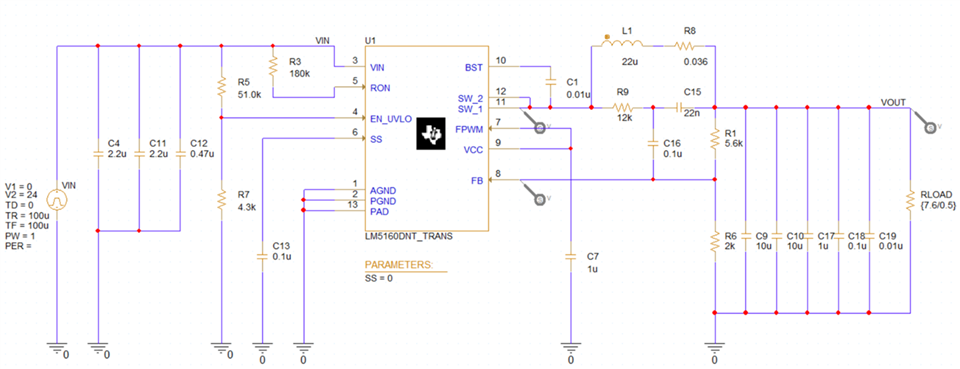

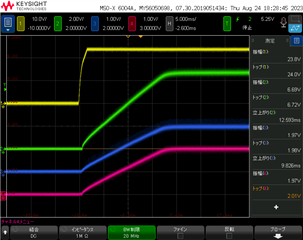

我使用与 PSpice 模型相同的电路图测量了启动。

(Vout 略有不同、但包括 CSS 在内的所有其他电路都是相同的。)

实际的上升波形没有产生 Css 以外的任何延迟:0.1μF = 20ms。

您能告诉我导致延迟的情况以及实际上发生了8ms 延迟的情况吗?

或者是否只能在 PSpice 仿真中发生这种情况?

※CH1:VIN、CH2:Vout、ch3:VSS、CH4:VFB

IOUT 条件为1A、0A 和500mA 处的波形几乎相似。

此致、

聪

尊敬的 Satoshi San、

该模型中没有固定的8ms 延迟。 在 SS 电压达到2V 之前、SS 电压是反馈基准电压。 SS 达到2V 后、内部2V 基准接管作为反馈基准电压。 根据负载条件、您可能会看到也可能没有看到一些输出电压延迟。 另请注意、电流限制也会影响 Vout 上升时间。 在该模型中、电流限制按其典型值进行建模、但您使用的 IC 可能具有比该模型更高的电流限制。

为了进一步研究这一点、您可以在仿真中的启动期间监测电感器电流和 SS 电压吗?

谢谢。

友好

尊敬的 Taroimo-San:

谢谢。 奇怪的是、当 CSS=0.1uF 时、SS 在20ms 时应达到2V、因为 ISS 为10uA、这是一个简单的数学方法。 不过、仿真结果使 SS 达到20ms 需要更长的时间。 恐怕 PSpice 模型内部有一些路径可用于建模、但它可能会从 SS 节点获取一些电流。 您能否监控 CSS 充电电流、看看它是否为10uA? 抱歉、此模型是9年前开发的、 调试模型可能需要一段时间。

除此之外、仿真结果看起来不错。

此致、

友好

你好,你好

感谢您的建议、

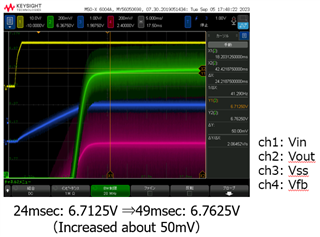

更新实际测量的波形。

通过扩大 Vout 范围和测量、实际波形也显示 Vout 在 TSS 后逐渐增大:20ms。

我们能够确认实际波形与 TI 的 PSpice 是匹配的。

但是、从 VSS 切换到 VFB 控制后、Vout 会随时间逐渐增加的原理我还是不明白的。

您能否提供有关此控制方法的更多详细信息?

或者是否有任何相关的应用手册?

此致、

聪

您好,Satoshi-San,

首先非常感谢您提供的信息。 ISS 波形真的很有帮助、它解决了我昨天的难题、让我想起了电路 是如何工作的:Iss=10uA 是电流源标称值。 由于电流源由内部固定电压轨供电、因此当 VSS 上升时、其工作电压净空会降低、而拉电流会降低。 当电压达到2.0V 时、不再需要提供10uA 电流、因此 将 VSS 保持为高电平。 由于降低了10uA、通过固定的10uA 和0.1uF Css 计算得出的纯数学运算将比实际性能短。

关于 Vout 延迟、如果先跟随 Vss、则遵循内部固定2Vref。 实际上、该波形显示了非常好的 SS Vout 跟踪。 另请注意、电路在闭环中运行、将会有延迟才能稳定至最终调节点。

谢谢。

友好