您好、TI 工程师、

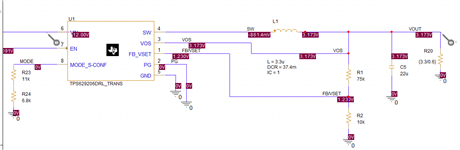

我正在使用输入电压为12Vdc、输出电压为5Vdc 的 PSPICE 模型进行仿真、但输出电压不是12v、这是我第一次使用 PSpice、设置是否有问题?

我已经确认电路板上的实际电路的输出电压是5V。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Onishi:

您的仿真结果看起来很奇怪。

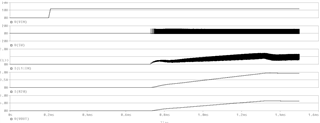

我采用相同的设置和结果如下所示。 输出电压为正常的5V。

您能否将仿真波形作为我的波形附上?

BTW、您选择的频率为1M、电感器为3.3uH。 电感器电流纹波的计算公式为(Vin-Vout)* Vout/Vin/L/FSW=0.884A。 此外、您设置的输出电流为5/(3.3/0.6)=0.91A、但 TPS62906是一个600mA 器件。 它可能会触发过流保护、因此我不建议您在此应用中使用3.3uH 电感器。

尊敬的 Onishi:

是的、我使用了脉冲电源。

实际上、我在 TI.com 上刚刚使用了 TPS629206的 PSPICE for TI 模型、并按以下文件更改电阻器。

e2e.ti.com/.../TPS629206_5F00_PSPICE_5F00_TRANS.zip

您可以尝试运行该仿真、看看有什么区别。

您是否编辑了仿真设置? 您可以直接向我发送仿真文件。

至于频率、您选择11k+6.8k=17.8k 模式电阻器、这样每个数据表的频率就为1MHz。

但我们仍然应该注意电感选择。 通常、我们会将电感器电流纹波设置在额定电流的40%以内。 然后、我来回顾一下您的原理图。

尊敬的 Onishi:

UVLO 不仅由 VIN 决定、还由 EN 的电压决定、因为 Vin 和 EN 之间有一个分压电阻器。

在仿真中、上升阈值为1/90*(90+470+430)=11V、下降阈值为0.9/90*(90+470+430)=9.9V。

![]()

迟滞为1.1V。

要计算 UVLO 迟滞、如果对 EN 使用分压器、则可以使用0.1V / Rbottom *(Rbottom + Rtop)。

如果 EN 保持高电平、则 UVLO 由 Vin 决定、迟滞为200mV。

尊敬的 Onishi:

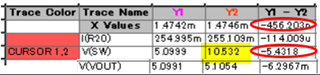

SW 的输出是降压输出的 PWM。

实际上、duty=[Vout + Iout *(电感器_DCR + Rdson)]/ Vin。 该值高于 Vout (5.1)/Vin (12)=41.6%。

您测得的波形是合理的、因为输入在12VDC 下不稳定。 可以看到、当高侧 MOSFET 导通时、SW 会出现压降。

在您的仿真中、SW 最大值为10.532V、因此占空比 D=5.1/10.532=48%也是正常的。

该主题已是13天。 如果您有与原始主题不相关的新问题、请创建新主题、谢谢!