大家好、我在 PCB 设计中使用的是 TPS71750DSER LDO 稳压器。 我正尝试在 LTSPICE 仿真中对输出端的噪声进行仿真。

在 LTSPICE 仿真期间、器件的模型文件"TPS71750_TRANS.lib"是否能够正确地将噪声包含在器件中?

我运行的是两者。 噪声和。 TRAN 仿真、我希望确保在整个电路中正确仿真现实生活部分的实际噪声、或者我是否必须引入第二个噪声源或定制噪声源并将其添加到电路中?

谢谢!

Johnathan Williams

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、我在 PCB 设计中使用的是 TPS71750DSER LDO 稳压器。 我正尝试在 LTSPICE 仿真中对输出端的噪声进行仿真。

在 LTSPICE 仿真期间、器件的模型文件"TPS71750_TRANS.lib"是否能够正确地将噪声包含在器件中?

我运行的是两者。 噪声和。 TRAN 仿真、我希望确保在整个电路中正确仿真现实生活部分的实际噪声、或者我是否必须引入第二个噪声源或定制噪声源并将其添加到电路中?

谢谢!

Johnathan Williams

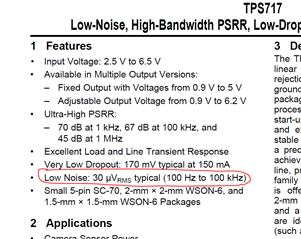

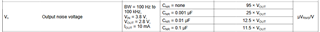

我懂了。 因此、如前所述、我将使用 该产品的 TPS71750DSER 版本。 基本上我有一个5.7V 的输入、输出电压为5V。 我们的降噪电容器为10nF、在器件的输入和输出端都有一个1uF 电容器。 大概是我从该 LDO 汲取的总电流是35mA。 此外、我们的预期信号带宽为15kHz 至300kHz、而不是列出的100Hz-100kHz。 在数据表上、我看到从100Hz 到100kHz 的总噪声(对所有来自白噪声、闪烁噪声等的各个噪声源求和)为30uVrms。 此值是否仍然适用于我们将使用5V 输出和35mA 电流消耗的 LDO 实施?还是我应该使用不同的噪声 Vrms 值?

尊敬的 Johnathan:

请记住、LDO 中的主要噪声源是电压基准本身、它由误差放大器根据您的输出电压设置进行增益处理。 因此、您将需要使用此 EC 表片段来帮助计算行业标准频率范围(10Hz - 100kHz 或100Hz - 100kHz)内的噪声:

我们没有该器件的特征值高于100 kHz。 您是否有需要满足的目标噪声规格? 我们可以推荐测量值高于100kHz 的较新器件。 如果您需要使用此 LDO、那么我们为您进行测量将会更容易。 您的预期输出电容是多少?

谢谢。

斯蒂芬