Other Parts Discussed in Thread: TPS6521905, AM6412, TPS22965

主题中讨论的其他器件:AM6412、 TPS22965、TPS6521905

大家好!

我必须研究为 Sitara AM6412供电的尽可能紧凑的解决方案、我找到了一些可能适合这种情况的 PMIC 基准。

( 唯一未使用的接口是 QSPI、PCIe、UART)

以下是有关 TPS6522053和65219型号(从01至08、加上0C)的一些问题。

1 -因为有很多变体,是否有文档解释这两个部分之间的区别?( SLVAFE9在6521904停止)?

2 -您能否解释 FSD 功能在 TPS6522053和 TPS6521901至04上默认启用的用途。

-"第一"是指:部件第一次看到功率,还是意味着每次看到功率,因此绕过 EN 输入信号控制(我们确实需要一个使能控制)?

- FSD 可能只适用于 I2C 功能,它必须连续运行,而不是直流/直流和 LDO 功能。 请说明。

3-在所有的变体中有一个可以编程"在家里"?

4 -对于默认情况下启用此功能 但在家中无法编程的部件,我们如何禁用 FSD?

5 -使用3V3 LDO1输出为 AM6412 3V3引脚(例如 VDDSHV_MCU 等)供电时、有什么问题(考虑到总电流< 400 mA) ? 所有示例都使用一个额外的 TPS22965

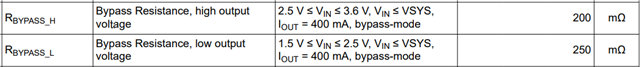

6-相对于 LDO1、您能解释一下"旁路"与"负载开关"的概念吗? 。 当 LDO-VIN=3、3V 和我们希望 LDO-Vout=3、3V 时是否相同?

7-假设 LDO-VIN = 3.3并且 LDO1配置为旁路模式(默认),我们是否应该期望 LDO1-LDO1 VOUT 等于3.3-0.2*0.4 (由于旁路电阻)= 3.22V? 或者我们应该考虑损耗至少为300mV 的压降吗?

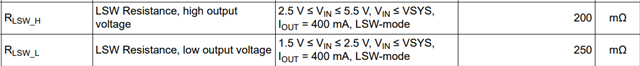

8 -同样的问题当 LDO1配置为负载开关模式时:只有0.2欧姆 Rswitch 必须考虑?

9 -在 SKAM64 EVM 中、我们可以注意到、尽管 TPS6522053采用"By_default"旁路模式、但 LDO1_VIN=3.3V 期望 LDO1_VOUT=3.3V。 这是如何管理的?

此致、

布鲁诺