请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMZM33602 主题中讨论的其他器件: UCD9081

大家好!

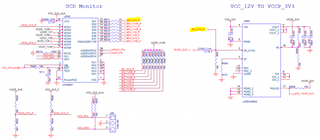

我们在设计中使用 LMZM33602电源模块。 请查看所附原理图片段的同步连接。

由于该引脚连接10K 下拉电阻、因此 LMZM33602默认为禁用状态。 稳压器 IC 将通过 UCD9081电源管理器 IC 驱动的3.3V 信号启用。 由 FPGA 生成的 LVCMOS (3.3V) 240KHz 时钟将通过交流耦合电容连接到 EN/SYNC 引脚。 请告知我们、原理图连接和电压电平是否适合使用 EN/SYNC 功能。 如果需要降低 UCD9081 IC 产生的电压以满足 EN 引脚的最大电压、我们还提供了电阻分压器选项、通过在 UCD 使能输出线路上放置串联电阻器。 请告诉我您对改进设计和电路工作的建议。