Other Parts Discussed in Thread: TINA-TI

我们正在着手一项关键设计、其中转换器稳定性必须是优先事项、并且在仿真期间、我们遇到了输出电压的奇怪行为。 Spice 模型(在 LTSpice 中仿真)和 Webench 中均存在该行为。 该问题不会在 Tina TI 的仿真中出现。

您能否告诉我们、输出电压的这种行为是否会在实践中实际发生、或者它在仿真模型中是否存在某种问题?

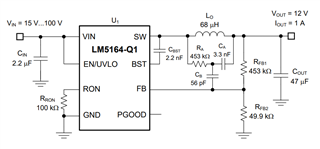

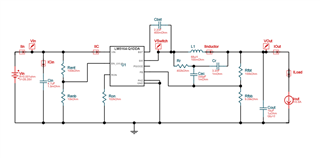

转换器规格为:

输入电压:16.5至40V (标称值为36V);

输出电流标称值为0.2A、最大值为0.8A。 我们将其设计为0.8A 以减少电容器-运行仿真得到的输出电流为0.8A。

输出电压:14.5V

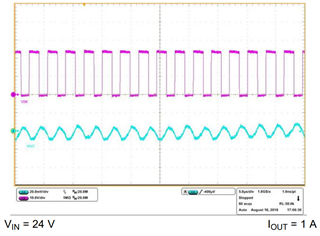

发现的波形:

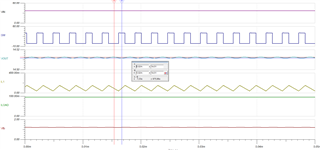

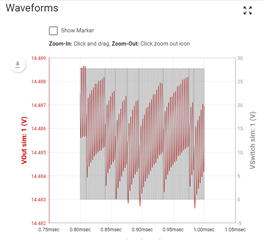

Webench:

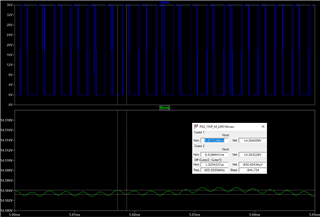

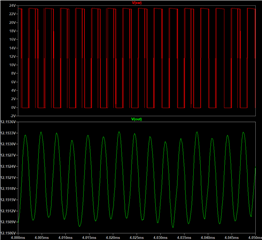

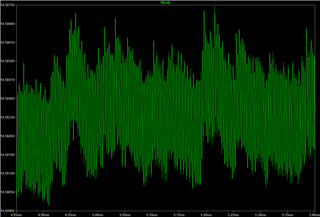

LTSpice:

仿真电路:

我理解垂直跨度很小、但这些变化让我们担心系统的稳定性。

提前感谢您!