主题中讨论的其他器件:LM5157

您好!

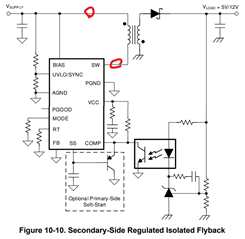

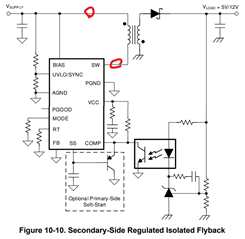

您是否会建议 在以下两个点添加旁路电容器。

如果我们可以添加、可以添加任何参考? 电容器的最大值限制是多少?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

您是否会建议 在以下两个点添加旁路电容器。

如果我们可以添加、可以添加任何参考? 电容器的最大值限制是多少?

尊敬的 Feng:

感谢您使用 e2e 论坛。

在反激拓扑中、由于电感器的原因、SW 引脚上的过冲确实会更高。 建议在原理图中标记的两个点放置一个缓冲器。

这种情况下通常使用 RCD 或二极管缓冲器。

一个参考是我们的 EVM 设计:

https://www.ti.com/tool/LM5157EVM-FLY

您还可以在我们的设计库中查看其他参考资料:

https://www.ti.com/reference-designs/index.html

对于缓冲器的值、可以使用合适的基准或计算值。

对于计算工具、我强烈建议功率级设计器:

https://www.ti.com/tool/POWERSTAGE-DESIGNER

此致、

尼克拉斯