您好!

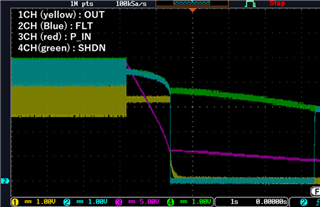

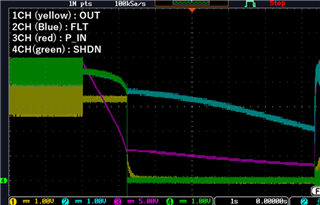

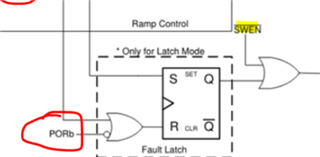

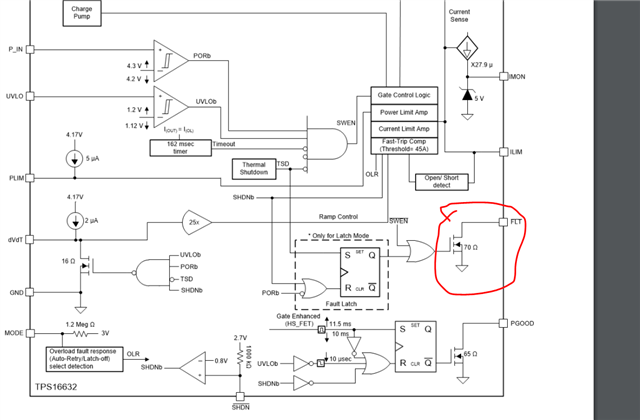

以下 E2E 论坛讨论 FLT/SHDN。 论坛解答指出:"当 SHDN=LOW 时、器件不会置位 FLT、因为它不是故障场景。"

[问题]

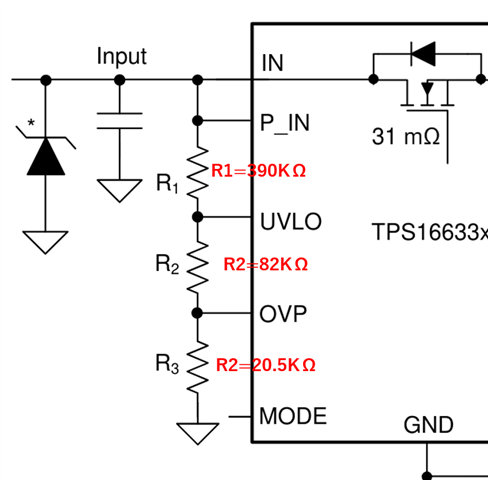

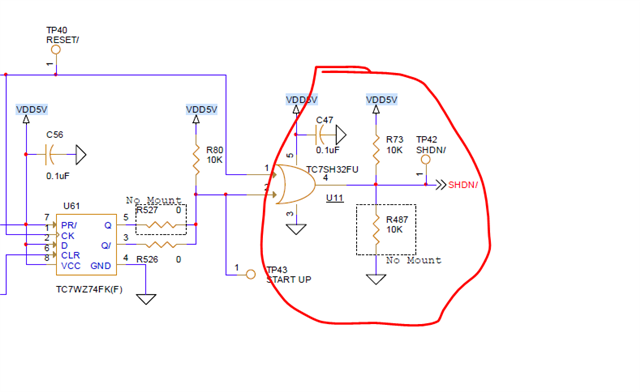

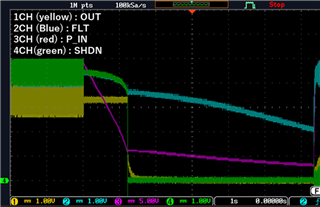

在通过关断功能关闭内部 FET 后、UVLO 是否工作、FLT 是否置位为低电平?

或者、当该器件被关断功能关闭时、UVLO 不工作且 FLT 未置位为低电平?

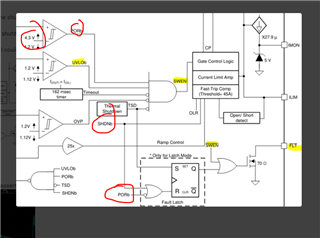

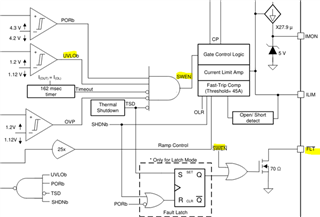

查看内部方框图、我找不到任何依赖关断功能来确定 FLT 是否置位为低电平的电路。

增编

客户想知道为什么在通过关断功能关闭内部 FET 后、ULVO 不会将 FLT 置为低电平。

此致、

科诺