Other Parts Discussed in Thread: LM25011

大家好、

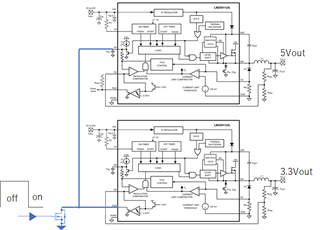

3.3V 和5V 通过连接的电路配置生成。

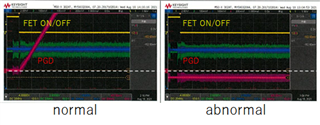

即使将输出3.3V 电压、3.3V 侧的 PGD 也不会变为高阻态并具有负电压。

是什么导致 PGD 偏置为负电压?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.