您好!

我按照 SLUR664的原理图实现电路、此电路运行良好。 根据应用的不同、我已将 SR MOS 和相对电路更改为二极管(HTS10U60)。

我发现输出在无负载的情况下保持开启和关闭。 我已检查过 Vdd、并发现在休眠200毫秒左右后、它将下降到8V 或更低。 我试图增加一些负载、但没有得到更好的效果。 我想知道 Vdd 会有多大的下降。 非常感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我按照 SLUR664的原理图实现电路、此电路运行良好。 根据应用的不同、我已将 SR MOS 和相对电路更改为二极管(HTS10U60)。

我发现输出在无负载的情况下保持开启和关闭。 我已检查过 Vdd、并发现在休眠200毫秒左右后、它将下降到8V 或更低。 我试图增加一些负载、但没有得到更好的效果。 我想知道 Vdd 会有多大的下降。 非常感谢。

尊敬的 Mujtaba:

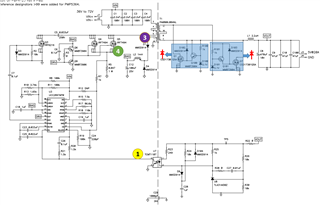

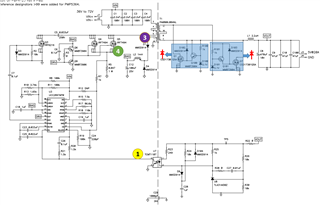

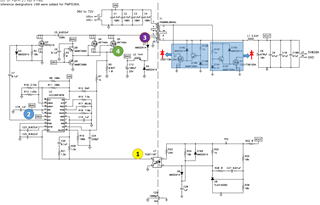

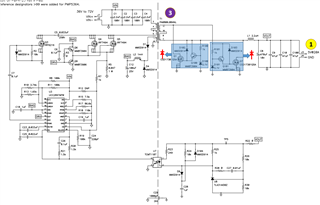

原理图中显示了图 I 发布的 CH1、3、4。 CH1是光耦合器的反馈信号。 CH3是变压器的偏置匝数(引脚1)。 Ch4是连接到 VDD 的 BIAS 信号。

这是您提到的波形。 我添加 CH2作为 IC 输出引脚(DRV 信号)

CH1:FB

通道2:IC 输出(DRV)

CH3:辅助绕组电压

通道4:VDD (BIAS)

数字显示了相应的测量 位置。

以下波形处于不同的时间刻度或时间周期下。

1.

2.

3.

4.

5.

6.

7.

8.

感谢您的答复。 如果需要更多的波形、请告诉我。

谢谢。

莱奥

尊敬的 Mujtaba:

抱歉、我们没有差分探头。 我无法在同一图中显示初级和次级。 我将分别进行展示。 我们来看一下次级变压器的波形、希望波形能够显示初级侧对应的相对计时周期信息。

我发现我之前将 C23设置为0.22uF (这意味着我之前发布的是在 C23=0.22uF 条件下)、然后我将其改回0.033uF。 VDD 的平滑部分似乎消失了、而 VDD 保持充电和放电。 这里是波形。 CH1是输出(5V)、CH3是变压器(次级)的引脚11。

感谢您的答复。 如果需要更多的波形、请告诉我。

谢谢。

莱奥

尊敬的 Mujtaba:

很抱歉迟到了回复。 许多部件 在实验中进行了更换、其中一些部件因事故被损坏。 使我的电路与原始电路不同。 因此我无法获得与之前类似的波形。

但是、我发现了导致 Vdd 下降的问题。 随着输入电压升高、 变压器的辅助匝数将产生较低的电压。 这似乎会导致 VDD 低于8.5V。 一旦输入电压降低或输出电压略有增加、Vdd 将更稳定。

您可以关闭该主题、感谢您的帮助。