大家好、

这是 Jerry。

现在我的客户在他们的设计中使用 UCC21220DR、他们发现在经过耐受电压测试后、引脚1和引脚2都短接到引脚4。 其测试条件为将系统的输出连接在一起、然后在输入侧施加4242VDC、5s。

因此、他们想知道可能是什么原因导致引脚1和引脚2与引脚4短路。

祝你度过美好的一天!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您能否提供测试电路原理图来帮助我直观地展示4242Vdc 的应用情况? 在此测试之前、所有输入引脚通常在外部短接在一起、这应该可以防止它们出现引脚对引脚过压?

此致、

肖恩

P.S。高电压测试的有用文档如下: https://www.ti.com/lit/wp/slyy063/slyy063.pdf

你好、Sean

感谢您的解释、以下是我们客户设计的

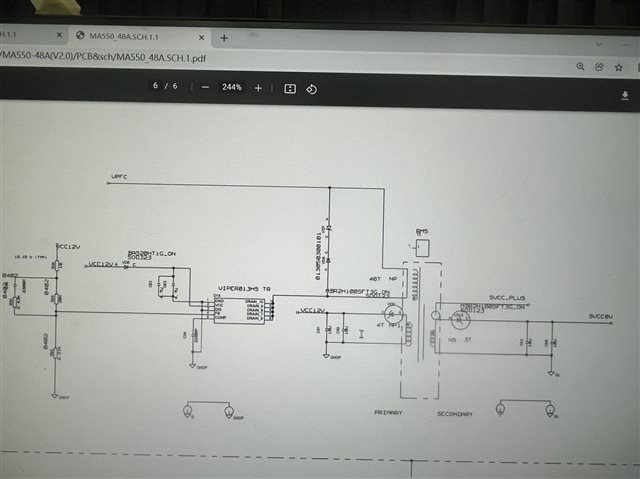

上图是主电源拓扑的原理图、使用 PFC (BOOST)+LLC 拓扑、使用红线绘制了 PFC 的电感和电容。 红色圆圈标出了由 UCC21220驱动的 LLC 初级侧使用的 MOS。 和1、2和3在进行测试时短接在一起、并直接在1上施加4242VDC。

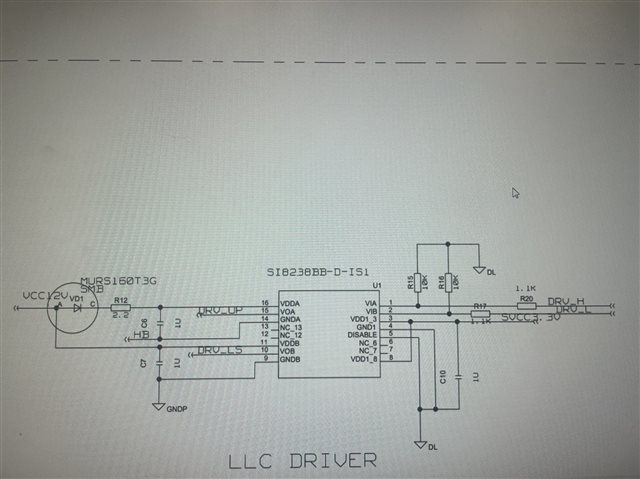

上图是驱动器电路、DRV_H 和 DRV_L 连接到 MCU、DRV_UP 和 DRV_LS 连接到 MOS 的栅极、如主电源拓扑中所示。 12V 是从220VAC 转换而来的、如下所示。

如果您有任何其他问题、请随时告知我。 谢谢。