主题中讨论的其他器件:TPS62822、 TPS62903

我们的客户使用的是其电路板上带有 AM243x 的 LP87334D。

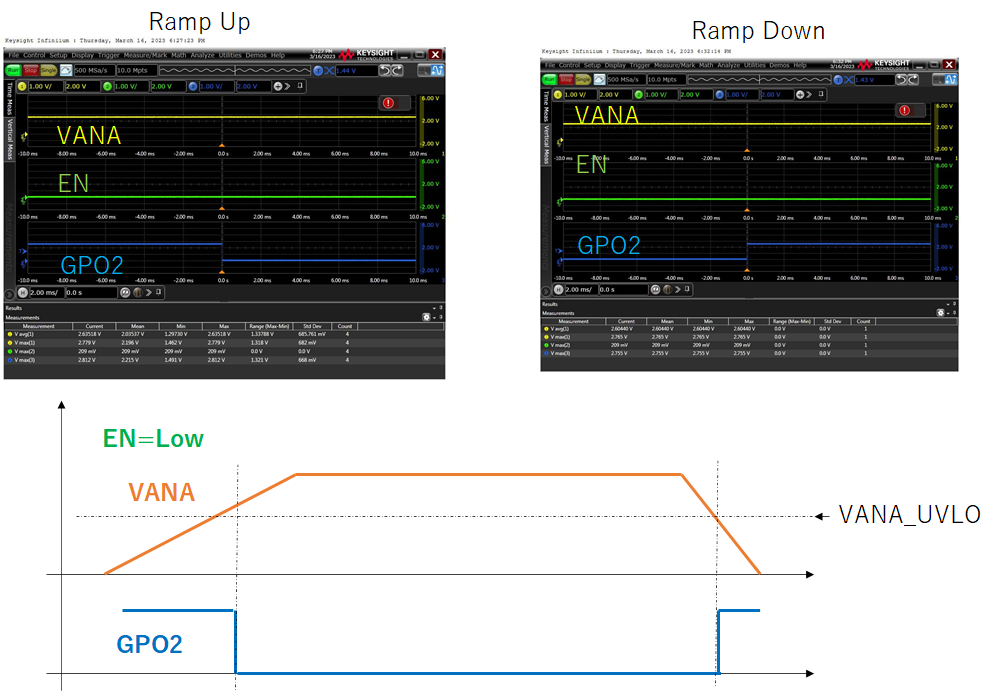

GPO2输出信号在关断后似乎浮动了大约800us。

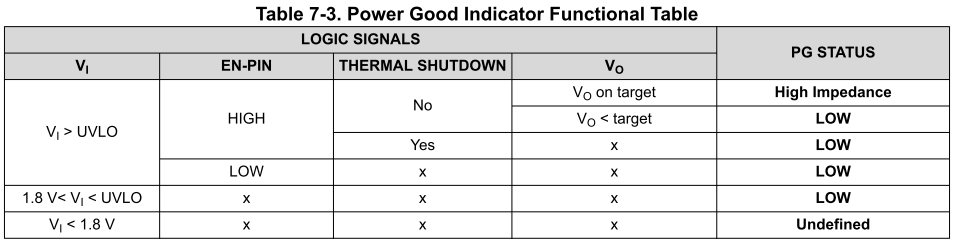

在 LP87334D 数据表的"7.3.7器件复位场景"中、介绍 VANA 电源电压降至 UVLO 阈值电平以下时的行为:

"如果 VANA 电源电压低于 UVLO 阈值电平、则禁用所有稳压器

立即、GPO 或 GPO2信号被驱动为低电平 ,所有寄存器位都将重置为默认值。

当 VANA 电源电压转换为高于 UVLO 阈值电平时、会发生内部 POR。 该 OTP

这些位会加载到寄存器中、并根据寄存器设置启动。"

GPO2输出信号在关断后约800us 浮动是正确的吗?

如果正确、LP87334D 的 EN 输入信号和 GPO2输出信号将进行与操作并输入到 TPS62822的 EN。

此致、

大辅