您好 TI

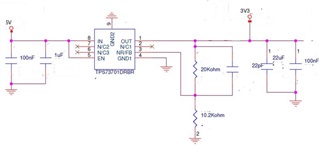

我的设计是附加电路、EN 引脚和5V 连接在一起。 在5V 和3V3放电至<0.01V 后、IN 和 OUT 引脚将短接几分钟。 我知道 EN 引脚和 Vin 引脚连接在一起会导致这种 现象。 是否有人建议 缩短这一 现象? 例如,放电顺序?

谢谢你。

林姜

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 TI

我的设计是附加电路、EN 引脚和5V 连接在一起。 在5V 和3V3放电至<0.01V 后、IN 和 OUT 引脚将短接几分钟。 我知道 EN 引脚和 Vin 引脚连接在一起会导致这种 现象。 是否有人建议 缩短这一 现象? 例如,放电顺序?

谢谢你。

林姜

林金杰,

我对你所问的问题感到困惑。

如果 IN 和 EN 短接在一起、则器件将尝试在中所有高于使能阈值的点运行。

Unknown 说:5V 和3V3放电至<0.01V

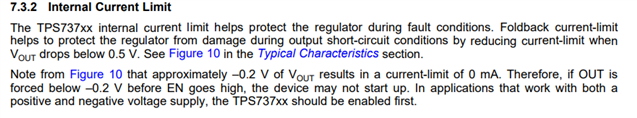

这是输出对 GND 短路情况。 在这种情况下、通流器件在完全打开时将输入对输出短路、并尝试重新调节器件输出引脚上的电压。 这会导致电流限制踢进:

如果输出短接至 GND 或被拉至低电平、则器件可能会开始循环进入和退出热关断。

为什么输出被拉至低电平? 什么负载条件强制输出降至<0.01V?

此致、

约翰

您好、John

5V 和3V3放电至<0.01V ->这是我们的断电顺序:1. 移除输出负载。 2.将5Vin 放电至<0.01V。 3.将3V3 Vout 放电至<0.01V。 在完成断电序列后、 我们发现 Vin 和 Vout 将保持短路 (低电阻)很长时间(大约几分钟)、然后恢复到高电阻。 我认为是 Cgs 的 MOS 之间的 Vin 和 Vout 造成的现象。 有没有加快断电顺序的建议?

谢谢你。