您好!

我打算在我的设计中将 TPS2663 (1)用作电子保险丝、在两个电源轨上提供 OVP、UVLO 和反向保护。

我将在 PSPICE 中对此进行仿真、但发现 UVLO 似乎未在所需电压下激活。

OVP 功能正常。

在电压低于我的预期值之前、UVLO 不会激活和置位 FLT。

OVP 激活时为30V、我希望 UVLO 激活时为20V。

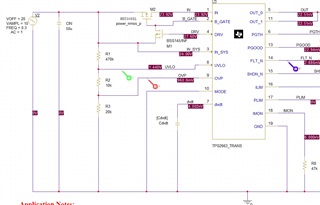

此部分电路如下所示。

根据数据表参数选择 R1、R2和 R3的值、以设置 UVLO 和 OVP。

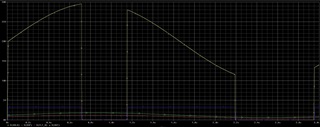

我的仿真结果显示、在30V 左右可正确激活 OVP。

当 UVLO 引脚<800mV (阈值应为1.12V 下降)时、在输入(和输出)电压降至12V 以下之前、UVLO 不会触发。

有什么想法、为什么会出现这种情况?

如果这只是我在现实生活中在器件中看不到的仿真怪异行为、我对此很满意、但我也很困惑为什么仿真中会这样做!

感谢您提出任何想法。

提前感谢!