工具与软件:

您好!

我想问您 VSW 下降时 UCC28782的行为。

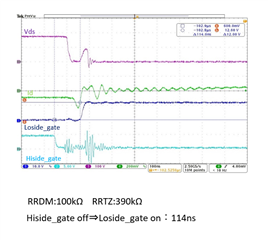

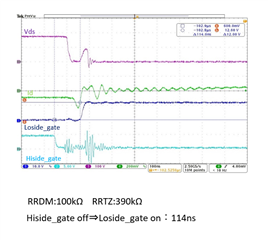

随附的图显示了 VSW (VDS)下降时的波形。

当低侧导通时、VSW 再次上升。 该器件用红色圈出。

我想删除用红色圈起来的这部分、是否有办法做到这一点?

我还认为、可以通过扩展 Tz 来消除用红色圈出的器件、因此我将 RRTZ 从240kΩ 更改为390kΩ。

然而,Tz 根本没有延长。 如果 Tz 没有变化、请告诉我。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我想问您 VSW 下降时 UCC28782的行为。

随附的图显示了 VSW (VDS)下降时的波形。

当低侧导通时、VSW 再次上升。 该器件用红色圈出。

我想删除用红色圈起来的这部分、是否有办法做到这一点?

我还认为、可以通过扩展 Tz 来消除用红色圈出的器件、因此我将 RRTZ 从240kΩ 更改为390kΩ。

然而,Tz 根本没有延长。 如果 Tz 没有变化、请告诉我。

此致、

尊敬的 Kaji-San:

感谢您与我们联系。

1. Im +和 Im -似乎不寻常,等于2.2A。 谐振时间过长。 我想我们可能需要检查钳位电容器。 请尝试减小该值。

2. 如果 RDM 过高,则强制高侧开启时间将过长。 调谐器将无法完全补偿、从而会产生过多的负电流。 然后、这会增加正电流以补偿额外的功率损耗、并会进一步增加功率损耗。

如果 RDM 过低、则高侧 FET 可能会在变压器完全退磁之前关闭、从而中断有源钳位谐振电流并导致高侧 FET 和 SR FET 中的高开关损耗。 当调谐器来回尝试恢复理想开关点时、它会干扰调谐器的运行。

如果 RTZ 过高或过低、它会将低侧 FET 的导通点移动到漏极波形谐振谷的任一侧、从而产生硬开关、而不是 ZVS。

我认为我们需要对此进行调整、结合 Cclamp 值降低此值以获得最佳结果。

3.在高侧脉冲导通时、您可以尝试减缓低侧 FET 的导通吗、或许可以增加栅极电阻以查看这是否改善。

请告知我们您的观察结果。

此致、

哈里什

感谢您的答复。

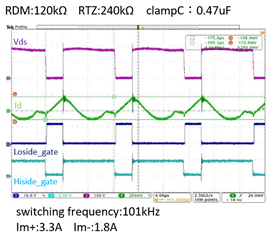

我调节了钳位电容器和 RRDM、并获得了以下波形。

我认为波形得到了优化、但您认为呢?

但是、与之前的变化相比、效率没有提高。

我们考虑这种情况的原因是为了提高效率。

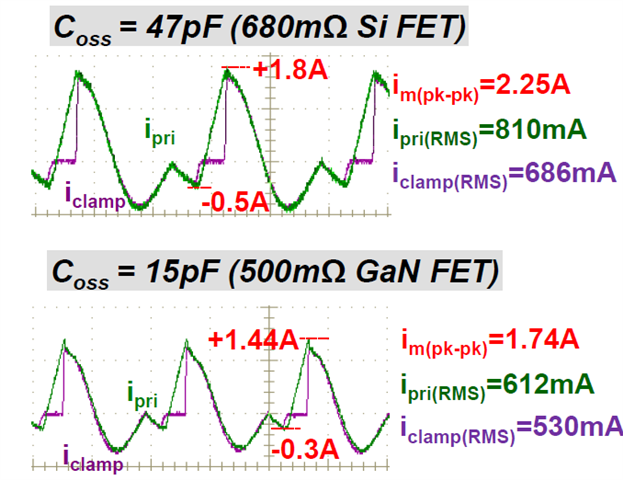

提高效率以降低 CSW 从而降低磁化电流的有效值的唯一方法是吗?

我知道、当 PWMH 关闭时、降低 CSW 会降低初级侧负电流。

但是、我不明白 PWML 关闭时初级侧电流降低的原理。

您能否解释一下背后的原理?

此致、

尊敬的 Kaji-San:

感谢您与我们联系。

我认为 RDM 和钳位电容器的调节现在好了很多初级电流。

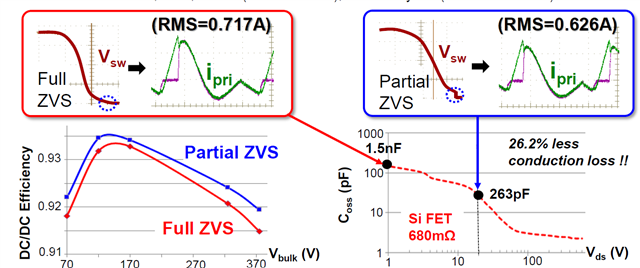

1.开关节点电容非常有助于降低初级侧的 RMS 电流。

2.您还可以尝试将整个 ZVS 调节到部分 ZVS 来查看这是否有用。 尽管与 Si 情况相比、可能不是 GaN 情况的最佳选择。

3. CLAMP 仍可进一步优化、以使谐振时间高于 PWM 导通时间、从而有助于产生 RMS 电流、因为1.8A 仍出现在较高侧。

总体而言、我认为 CLAMP、CSW、RTZ 和 RDM 仍可进一步调优、以优化效率。

此致、

哈里什

尊敬的 Kaji-San:

感谢您与我们联系。

是的、增大钳位电容器会增加谐振时间。 确保负 Imag 较小。 1.8A 似乎很高。

我认为优化应该遵循以下步骤:

因此、优化开关节点电容在这里会有所帮助。

2.使用 C CLAMP 的最佳值并根据 PWMH 导通时间进行调整。 可能谐振周期略高于 PWMH 导通时间。

3.优化 RDM 和 RTZ 电阻器。

此致、

哈里什