主题中讨论的其他器件:BQ79616、 UCC23511

工具与软件:

嗨、TI 专家!

我们正在设计一个与电池组之间双向电流流动的系统。

因此、我们使高侧的 FET 以背靠背拓扑排列、放电和充电 FET 源是公用的。

以下是我们要求澄清的要点:

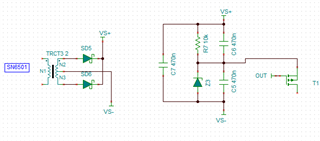

1)为了在高侧驱动 FET 的栅极、我们使用了光耦合隔离式栅极驱动器、通过该驱动器源极端子与逻辑侧隔离。

为此、我们使用了一种隔离式电源。

2)我们使用了一个预放电电路、其中包含一个与限流电阻器串联的 P 沟道 FET。 因此、由于预放电 FET 与放电 FET 并联、并且 P 沟道 FET 在栅极端子需要比源极端子更低的电势。 因此、我们使用了另一个光耦合隔离式栅极驱动器、通过将栅极接地和源极连接到 PDSG 控制引脚来实现相同的功能。

我们想知道电路是否能达到理想工作状态、或者是否需要任何优化或更改。

等待你对同样的宝贵答复。

谢谢、此致

Ibrahim

e2e.ti.com/.../32_2700_S_5F00_BMS_2D00_Gate_5F00_Driver_5F00_Current_5F00_Sense-_2800_2_2900_.pdf