工具与软件:

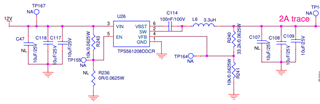

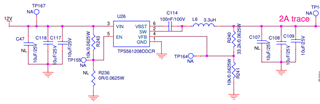

我们使用 TPS561208DDCR 将12转换为3.3V、如以下原理图所示。

在我们的用例中、我们注意到 IC 的 PMIC 行为在电路板的灌封条件下发生变化(灌封材料浇在整个电路板上)。

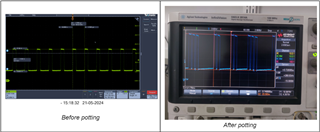

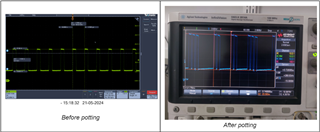

采用交流耦合方式且带有探头的3.3V 线路。

灌电流前后的开关引脚波形

灌电流前后的反馈引脚波形

灌电流之前和之后的自举引脚波形

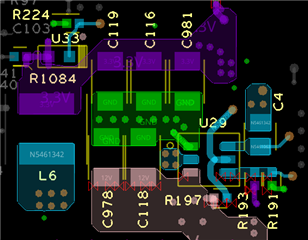

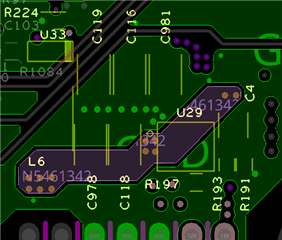

下面是灌封板的图像

此噪声会影响电路板上的其他敏感 IC。 有人能解释 PMIC 行为改变的原因吗?如何消除该改变?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

我们使用 TPS561208DDCR 将12转换为3.3V、如以下原理图所示。

在我们的用例中、我们注意到 IC 的 PMIC 行为在电路板的灌封条件下发生变化(灌封材料浇在整个电路板上)。

采用交流耦合方式且带有探头的3.3V 线路。

灌电流前后的开关引脚波形

灌电流前后的反馈引脚波形

灌电流之前和之后的自举引脚波形

下面是灌封板的图像

此噪声会影响电路板上的其他敏感 IC。 有人能解释 PMIC 行为改变的原因吗?如何消除该改变?

这些层中的每一层都由电源平面隔开、电源平面上有许多耦合电容器。 以下是堆叠:

顶部

电源

内层1

内层2

GND

底部

我们还有另一个类似原理图和布局的电路板、如下所示、此电路板存在0%的此问题、使用此布局已生产了超过20万至25万件产品、并且已在现场运行了4年。

3.3V 降压原理图

底层

内层2 (浅紫色平面将 PMIC IC U26的引脚2连接到电感器。

内层1 (连接到反馈电阻分压器的输出布线)

以上工作布局的堆叠情况

顶部

电源

内层1

内层2

GND

底部

此外、我们还尝试通过在组件之间手动焊接 pF 电容器来模拟灌封寄生电容、因此没有这种问题。

我们的实现方式与数据表布局建议非常相似

请建议是否存在其他原因。