工具与软件:

您好!

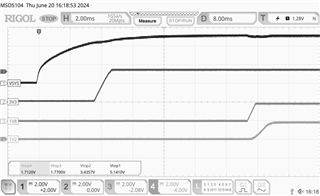

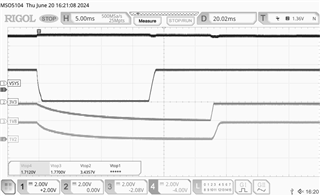

我们目前正在使用 TPS6521903 PMIC 为 SoC 供电的新模块上设计 AM6254 SoC。 在上电序列期间、电源轨按照 SLVUCJ2至 Buck3 (1V2)中的定义斜升、然后 PMIC 断电并在完全关断之前重试两次。 测量 Buck3 (1V2)电源轨后表明、它在 电源轨激活之前正将1V8反馈到电源轨上、从而导致 PMIC 停止、重试、最终终止上电序列。

请参阅 处理器论坛上链接发布的 am625-vdd_1v8-vdda_1v8-feedthing-on-vdd_1v2-rails-on-startup、了解更多详细信息以及为找到该问题而进行的各种尝试。

如果有任何见解、我将不胜感激。