Other Parts Discussed in Thread: CSD18514Q5A, LM5145, CSD18563Q5A

主题中讨论的其他器件: CSD18563Q5A、CSD18514Q5A

工具与软件:

尊敬的 TI:

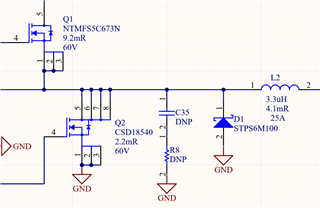

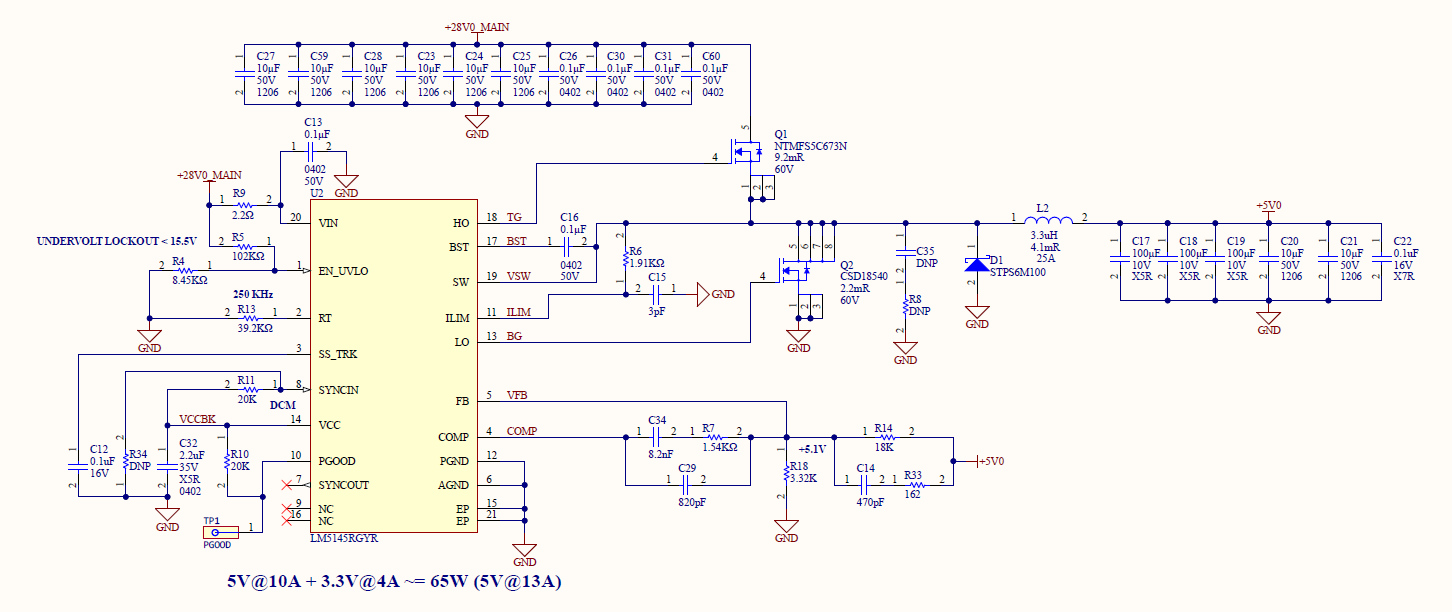

我们的65W 降压转换器设计基于 LM5145。 我们面临的问题是在启动时、我们具有非常轻的负载、小于100 mA。 稳压器在启动时似乎不稳定、正在烧断高侧 MOSFET。 目前、SYNCIN 引脚被拉至高电平、从而使我们进入强制 PCM 模式、该模式可能使电感器实现连续导通。 您是否建议通过将 SYINCIN 拉至低电平以非连续模式运行? 我们无法让稳压器运行足够长的时间来对此进行测试。 谢谢。