主题中讨论的其他器件:TPS51285A、、、 CSD17302Q5A

工具与软件:

嗨、团队:

客户希望其开关死区时间可以大于10ns 规格、

我知道这个问题也和 MOS Qg 有关、不过是固定了。

我们可以对原理图中的缓冲器值执行任何权变措施吗?

上方原理图:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

嗨、团队:

客户希望其开关死区时间可以大于10ns 规格、

我知道这个问题也和 MOS Qg 有关、不过是固定了。

我们可以对原理图中的缓冲器值执行任何权变措施吗?

上方原理图:

Unknown 说:我们是否可以对原理图中的缓冲器值采取任何变通办法?

开关节点缓冲器不会影响 UGATE 至 LGATE 死区时间。

您是否知道 Sinopower 高侧 MOSFET 的器件型号和规格? PK600AB 器件号出现了一个来自其他制造商的器件、看起来它应该在20ns 内关闭。

该 MOSFET 关断和开关节点下降大约需要35ns、这对于1.9Ω 驱动器下拉在 PR4508 = 0Ω 的情况下对高侧 MOSFET 放电来说是很长的时间、而如此长的放电时间正是促成了从 UGATE 下降至 LGATE 上升死区时间的需要更多死区时间的原因。

还应注意、从同一栅极驱动器驱动2个 MOSFET 时、通常建议每个 MOSFET 都有一个单独的栅极驱动电阻、以便具有不同栅极阈值电压的 MOSFET 可以同时开关、并且具有较高阈值电压的 MOSFET 不会等到另一个 MOSFET 开关后才会开关。

尊敬的 Peter:

因此、它们具有主要来源 Sinopower 和 Nikosemi、

但两个电源都需要通过改变其他 MOS 来实现更大的死区时间。

客户更喜欢的解决方法,而不改变 MOSFET 优先,你有想法吗?

.

.

下面是 HS 和 LS MOS 均来自 Niko SEMI。

e2e.ti.com/.../084.00600.0B37_5F00_PK600BA_5F00_HS.pdfe2e.ti.com/.../084.PKCH6.0037_5F00_PKCH6BBWIC_5F00_LS.pdf

下面是 Sinopower HS 和 LS

TPS51285A 不提供用户可编程的死区时间控制。 死区时间只能由栅极驱动强度控制。 虽然我们可能会通过串联栅极驱动电阻器(目前在原理图中未提供)来延迟低侧 MOSFET 的导通、这可能会导致在 LGATE 关断和 UGATE 导通期间发生跨导。

也就是说、波形中显示的关断时间与 MOSFET 数据表中提供的栅极电荷和栅极电阻值并不相关、因此我建议更改自举电阻值和栅极驱动电阻值、并确保它们与原理图中列出的值相匹配。

即使栅极电阻为2Ω、驱动器下拉电阻为1.9Ω、从高侧 MOSFET 释放7.5nC 至8nC 的栅极电荷也不应花费35ns 的时间。 如果串联栅极驱动电阻器为0Ω、则可能需要查看栅极驱动和开关节点返回长度、以确定高侧 MOSFET 关断速度如此慢的原因。

我的道歉。 这应该是"检查"不变的

该原理图显示了 UGATE 至 MOSFET 栅极电阻器 PR4505和 PR4508的0Ω 电阻器以及自举电阻器 PR4507和 PR4506的1.5Ω 电阻器。 检查电路板上的这些电阻值以确保这些值正确。

是的、Richtech RT6575的死区时间比 TPS51285B 更长。 这种更长的死区时间会导致体二极管在每个开关周期中导通增加、MOSFET 功耗更高、并降低效率。

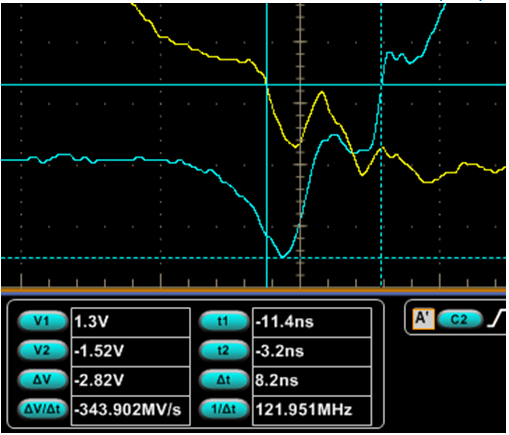

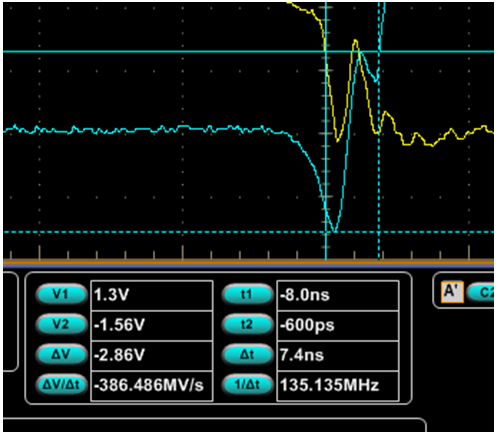

比较中非常奇怪的是、TPS51285B 和 RT6575的栅极驱动下降时间有显著差异、鉴于它们具有相同的驱动器强度、除非栅极驱动电阻不同、否则它们应该产生相同的下降时间。

Richtech 器件的波形显示12ns 下降时间。 我们对7.5nC MOSFET 的期望是通过1.9Ω 电阻和 MOSFET 栅极电阻1 -2Ω 从5V 放电。 除非串联电阻、焊点出现问题或器件损坏、否则在14ns 平坦区域下、我们不会期望 MOSFET 下降时间为37ns。

我建议对 UGATE 引脚、MOSFET 栅极引脚进行回流焊、并将 PR4505和 PR4508替换为0Ω 电阻器、以确保这些路径不会出现问题。 如果 TPS51285B 仍然显示 UGATE 下降时间37ns、请更换 TPS51285B、因为它可能已损坏。

那么我建议更改 TPS51285B、因为 UGATE 下降时间似乎不正确、并且器件可能已损坏。

尊敬的 Peter:

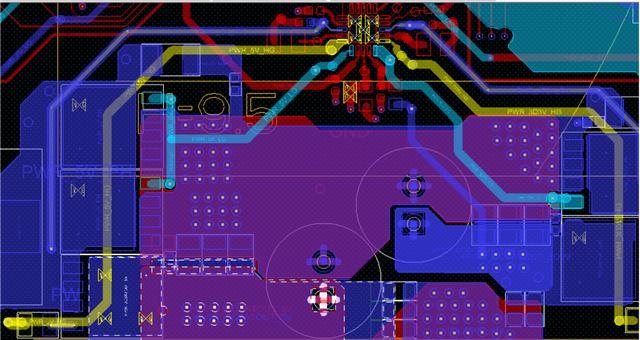

他们 在其他电路板上尝试了许多 TPS51285 IC、但看到的波形相似、因此这不是单个情况。 请检查下面的布局。

e2e.ti.com/.../242002_2D00_SC.0627WPH2213.7z

它们设法 在 LGATE 处插入1欧姆电阻器、但仍然无法通过 Lenovo 规格(8.2ns < 10ns)

此外、它们已将 HSMOS Qg 从13.5nC 更改为11.5nC、也会失败(7.4ns < 10ns)

客户提出的两个问题此时非常紧迫、如果布局考虑正常。

1.您为我们的控制器 HS MOS 建议什么 Qg 值?

您是否有建议的可以使死区时间满足规范的 TI MOSFET?

他们设法 在 LGATE 处插入1欧姆电阻器、但仍然无法符合 Lenovo 规范(8.2ns < 10ns)

Lenovo 为什么具有最小10ns 的死区时间规格? 这是一个任意且相当大的最小死区时间规格、会对其效率产生负面影响。

1. 您为我们的控制器 HS MOS 建议什么 Qg 值?

如您所述、较高的栅极电荷会导致 HS 关断速度变慢、从而缩短死区时间。

对于相同5mm x 6mm 8引脚热增强型封装的替代 TI MOSFET、我建议尝试 https://www.ti.com/product/CSD17302Q5A

它对5V 栅极驱动具有更低的 Rdson (从9 m Ω 到12 m Ω)、并且总栅极电荷(5.4nC 到8nC)要低得多

如果布局认为没问题。

布局看起来不错、但在一些地方还可以改进:

如前所述、当并联运行两个 MOSFET 时、通常最好在每个栅极驱动中使用一个单独的串联电阻、以允许 MOSFET 在开关转换期间具有不同的阈值电压。 这有助于平衡 MOSFET 之间的开关损耗和热性能。

布置 SW 连接、即尽可能多的栅极驱动路径的栅极驱动布线正下方高侧栅极驱动的回路、将更大限度地减少环路面积和电感、从而尽可能提供出色的导通和关断。

TPS51285B 使用自适应死区时间控制、其中在下降沿检测驱动器上的输出电压、 在开启互补驱动器之前开始12ns 或20ns 死区时间(在数据表中指定)。 确切的死区时间取决于检测后的 MOSFET 下降时间和互补的 MOSFET 上升时间。

由于驱动器在大约2V 的电压下检测到 UGATE 的关断、因此其是从2V 到0V 的栅极电荷、以及 LGATE 上升时间、而不是定义死区时间的总栅极电荷。

UGATE 下拉强度以1.9Ω 形式给出。 从2V 到0V、平均放电电流为0.5A、但目标规格为10ns 时、仅2ns 即可以0.5A 对 Vgs 进行放电。

LGATE 导通时间将增加一个约3ns 的短暂额外延迟、留下约5ns 或2.5nC @ 2V 的延迟、以便在死区时间小于10ns 之前关断高侧 MOSFET。 - CSD17302Q5A 在2ns 时具有1.5nC 的栅极电荷。

真正的问题是、Lenovo 的任意10ns 最小死区时间规格非常接近 TPS51285B 的标称12ns 死区时间规格。 如果有任何方法可以与 Lenovo 讨论10ns 规格、并说服他们为使用自适应栅极延迟死区时间控制(例如 TPS51285B)的控制器降低该规格、这将是更好的选择。

数据表中的12ns 是在栅极驱动器无容性负载的情况下测得的、因此没有斜坡需要应对。

它也不是从 SW 到 GND 测量、而是从 UGATE 到 LL (高侧 FET 的栅源电压)测量高侧栅极

如果测量开关节点在正负载下为负的时间段、可以很好地衡量实际反跨导时间。 对于内部 MOSFET 产品、我们通常会在5ns 至8ns 的时间内将该节点的栅极驱动调整为小于0.3V、以确保在最大限度提高效率的同时没有跨导。