工具与软件:

您好、先生、

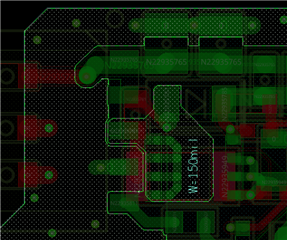

是否可以帮助您再次确认此布局是否可行?

e2e.ti.com/.../TPS23751-_2800_1_2900_.pdf

e2e.ti.com/.../DAP_2D00_X3060W_5F00_MB_5F00_20240904_2D00_pd.pcb

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、先生、

是否可以帮助您再次确认此布局是否可行?

e2e.ti.com/.../TPS23751-_2800_1_2900_.pdf

e2e.ti.com/.../DAP_2D00_X3060W_5F00_MB_5F00_20240904_2D00_pd.pcb

尊敬的 Diang:

在附件中、请找到我们从.pcb 转换而来的.brd 文件。

也许和最初的.pcb 存档略有不同、但我认为它与.pcb 存档非常相似。

请帮助查看它。 谢谢!

此致、

Ian

e2e.ti.com/.../DAP_2D00_X3060W_5F00_MB_5F00_20240905_2D00_poe.brd

您好、Ian、

感谢您的耐心。 请参阅以下评论:

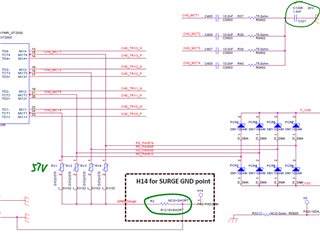

1.我可能不熟悉该应用、有一个奇怪、如果在安装 R2时、您的电路将有57V 额定浪涌压敏电阻与 Bob-Smith 端接(隔离额定值为2kV)并联。 在这种情况下、隔离电压会降级。 则可能无法满足802.3bt 隔离要求。

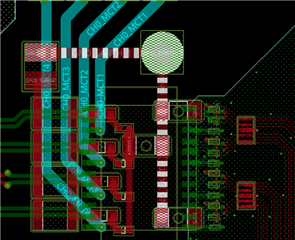

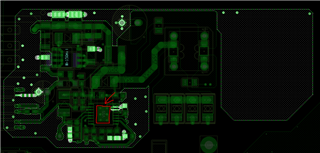

2.建议使 GND_EARTH 不跨越 PoE 线。 最好使用适当的入射距离创造清晰的边界。

3. Vneg 在内层的多边形覆盖了一些通孔。 TPS2374.72的 PAD 也存在问题。

4.初级侧 FET 与 Vneg 之间的距离太近。 请考虑增加到>0.6m 的距离以确保足够的间隙距离并减少噪声耦合。

此致、

Diang