Other Parts Discussed in Thread: TINA-TI, CSD85312Q3E

Thread 中讨论的其他器件:Tina-TI、

工具与软件:

尊敬的 TI:

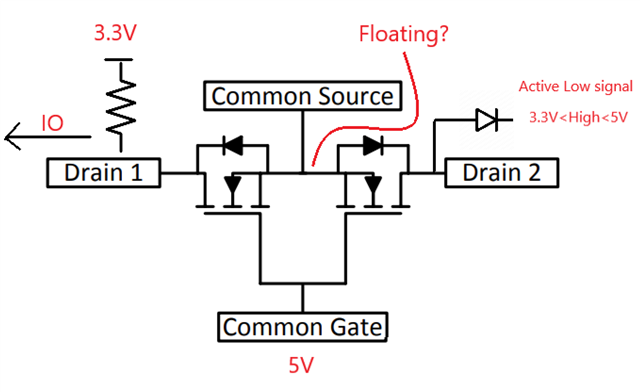

我有一个应用将使用背对背公共源 NMOS。

我想使用5V 来打开 背对背 NMOS、如果没有5V 电压、3.3V 就不会泄漏到 Drain2信号。 电路是否可以使用该功能?

此外、我知道 NMOS 开启条件是 VGS >Vth、但当 NMOS 关闭时、 它是否应该在两个源极引脚上悬空?

如果是、它如何工作? 这可能是一个基本的知识,但混淆了我很长一段时间, 如果你能帮助我清楚。