工具与软件:

您好、TI 专家!

我在使用驱动芯片 UCC21530-Q1时遇到了三个问题、需要您的专业建议、如下所示:

1.根据产品说明书第8.3.4章的内容、驱动器输出具有使用内部上拉 NMOS 的内部栅极电压增强器功能。 我的问题是何时打开上拉 NMOS 以及何时关闭上拉 NMOS?

2.如何判断是否适合打开上拉 NMOS、因为我觉得驱动芯片测量不到 MOS 的栅极电压就知道米勒电压下降的时间。

3.有一个异常现象:在双脉冲测试期间(下 MOS 作为目标器件,上 MOS 与电感短路),当增大 DC-link 高电压时,上 MOS 的栅极电压会下降到0V 以下,而不是0V。

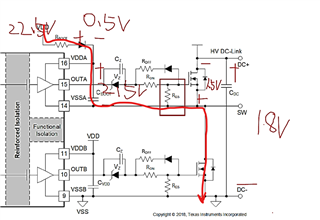

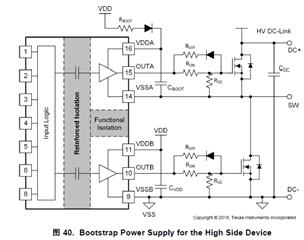

我们的驱动器设计与数据表中的示例电路相同、您可以参阅下图。

谢谢您~