主题中讨论的其他器件:、 TPS25947EVM、TPS25947

工具与软件:

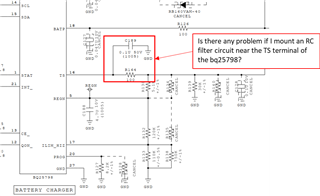

为了实现 ESD 保护、我想在 bq25798的 TS 线上实施一个 RC 滤波器电路。 (100Ω、0.1μF)

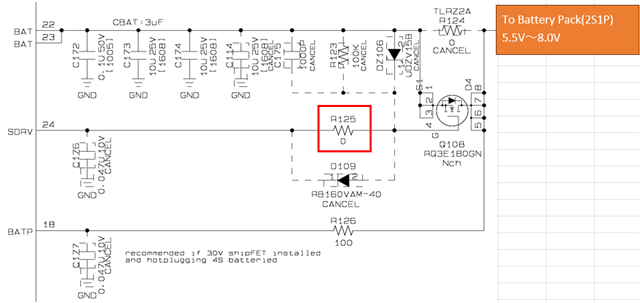

我考虑随附电路图中所示的配置、但如果您对该配置有任何疑问、请告知我。

此致、

Kagawa

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

为了实现 ESD 保护、我想在 bq25798的 TS 线上实施一个 RC 滤波器电路。 (100Ω、0.1μF)

我考虑随附电路图中所示的配置、但如果您对该配置有任何疑问、请告知我。

此致、

Kagawa

尊敬的 JEFF-SAN:

作为背景信息、我们正在设计一款采用可拆卸电池组的设计。 当移除电池包时、TS 引脚会暴露在外、因此容易受到 ESD 的影响。

基于上述背景、我们询问了 RC 滤波器的放置是否适合为 TS 引脚提供 ESD 保护、我们想要获得以下问题的答案。

・下面的 TI E2E 指出、不建议添加大于0.01uF 的电容器。 我们是否应该根据该线程中的响应将电流常数 C=0.1uF 更改为 C=0.01uF?

https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1325616/bq25798-esd-protection-bat-and-ts pins/5077719?tidearch=e2e-sitesearch&keymatch=bq25798%2520ESD%2520protection#5077719

此致、

Kagawa

尊敬的 JEFF-SAN:

下面是对目前为止在交换中安装在 TS 线上提供 ESD 保护的 RC 滤波器的电容的理解。

请确认这一理解是否正确。

1.不建议使用大于0.01 μF 的电容。

这是因为 RC 时间常量更大、并且充电在异常温度条件下停止工作所需的时间更长。

因此、充电可能会在适当的温度范围之外继续进行。

2. TS 线路电容器电容限值:可安装在 TS 线路上的最大电容为0.01uF。

3.充电关断时间的计算:TS 线路中 RC 滤波电路停止充电的延迟时间可通过以下公式得出:

τ= 3 * RC (τ:时间常数、R:电阻值、C:电容)

此致、

Kagawa

尊敬的 JEFF-SAN:

1) 1)在 TS 线路上安装 RC 滤波器电路是否存在任何问题?

如果以上情况不是问题、那么允许的最大 RC 时间常数是多少?

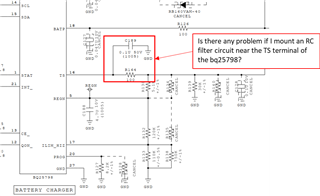

2) 2)在什么情况下需要安装 BQ25798EVM 中属于 DNP 的器件(D10、C42、R16、D9)?

这些元件默认不安装、但我想知道设计意图。

1.请告诉我们如何减少连接电池时的浪涌电流。

2.请提供您的意见、下图所示的电路配置是否足够、或者是否需要额外的元件。

bq25798连接到电池时允许的浪涌电流是多少? (BAT 端子、BATP 端子)

此致、

Kagawa

尊敬的 JEFF-SAN:

1. 您能否告诉我 TS 线上允许的最大 RC 时间常数是多少?

2. 我不完全了解需要 BQ25798EVM 的 DNP 元件(D10、C42、R16、D9)的情况。

请告诉我需要在哪些条件下实施这四个组件。

如果您能解释这些元件默认置于非安装状态的设计意图、我也将不胜感激。

3. 您提到"R125已设置为高于0Ω 以减慢 shipFET 的开通时间"。 这是指原理图上的 R125、这是否正确?

此致、

Kagawa

尊敬的 Kagawa:

关于1、TS 功能是比较器的梯形、因此增加 RC 只会减慢比较器的决策。 我们不使用 RC 进行测试。 停止充电之前的延迟是一种偏好、也可能是电池制造商对电池组高温或低温状态的限制? 我之前沟通过的数字来自使用过 RC 但未发现问题的其他客户。

关于2、如果使用 R17来减慢 shipFET 导通时间、D10可以缩短关断时间、因为它会使 R17短路。 D9可保护 shipFET 栅极至源极电压免受 SDRV 快速导通导致的过压影响(由于 SDRV 电流较小、因此不是问题。 C42简单地添加到 FET 栅源极电容会减慢导通/关断时间。 我不知道 R16的用途、但我不推荐它。

关于3、是的。

在 shipFET 上添加栅极至漏极电容器将进一步调整开通时间。

此致、

Jeff

尊敬的 JEFF-SAN:

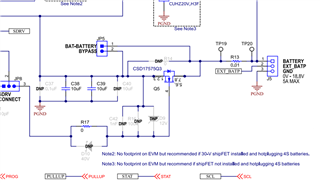

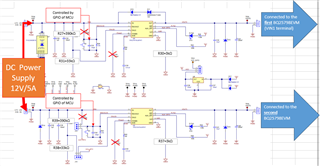

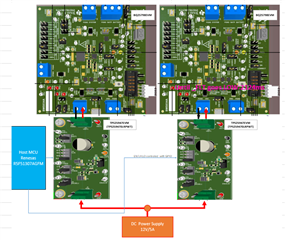

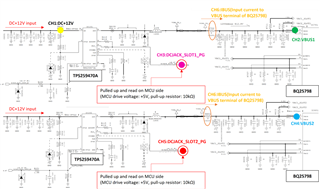

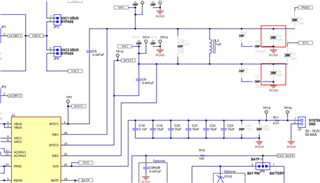

我们正在考虑将 TPS25947EVM 放置在 BQ25798EVM 输入之前的配置、以控制是否允许或禁止从主机 MCU 到 BQ25798的电源输入。

具体而言、BQ25798EVM 组装在数据表第31页图9-2所示的配置中、单输入端直接连接到 VBUS、而不使用 ACFET-RBFET、电子保险丝(TPS259470A)放置在 BQ25798EVM 的 VIN1输入侧。

然而、TPS259470A 的 FLTb 引脚在电源输入后下降、我们很难找到原因。

请注意、输入电源未处于过压/恒定电压/过流状态。

此外、断开 BQ25798的 VBUS 线路和 TPS25947EVM 的 VOUT 将停止此现象。

有什么想法、了解为什么 FLTb 在电源输入后脱落?

TPS25947EVM:

- OVLO 电压:15.38V 检测,13.97V 返回

- OVLO 电压:检测到15.38V ,释放13.97V

- ILIM 电阻:3kΩ(输入电流限制在1.11A)

-输入电源后_FLT 引脚瞬间掉电。

-输入功率低于 OVLO/UVLO/ILIM 阈值。

-可通过断开 BQ25798EVM 的 VBUS 线(VIN1引脚)和 TPS25947EVM 的 VOUT 引脚来解决该问题。

此致、

Kagawa

尊敬的 JEFF-SAN:

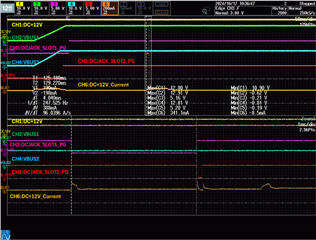

下面附加了其他电流测量结果以及电流原理图和测量点。

我们无法确定每个 TPS259470A 的 FLTb 引脚降至低电平现象的原因。

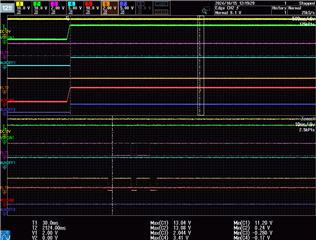

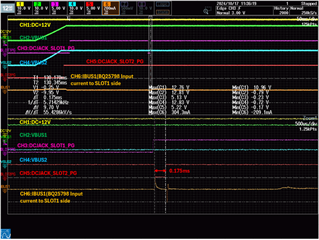

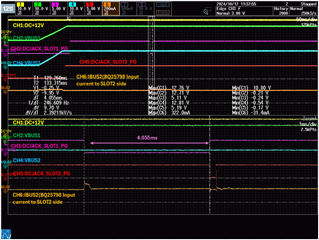

在将来自主机 MCU 的使能信号输入到 TPS25947EVM 的 EN/UVLO 后、FLTb 引脚降至低电平130ms。

ILIM_HIZ 引脚的电阻常数设置为 IINDPM = 1.25A。

我们已检查测得的波形、未发现任何过压或欠压情况、也未看到电流高于 BQ25798和 TPS259740A 规定的电流限值。

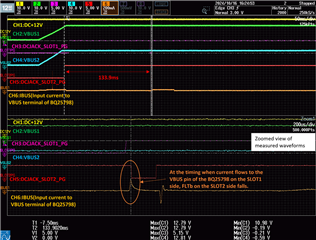

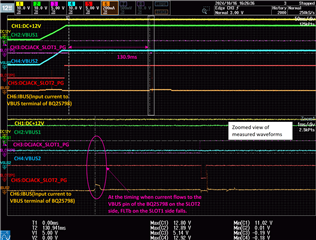

此外、下面的波形显示、当电流流向 SLOT1中 BQ25798的 VBUS 引脚时、SLOT2中 TPS259470A 的 FLTb 引脚在时序期间变为低电平。 也会出现反向情况。

如果 BQ25798的 VBUS 线和 TPS25947EVM 的 VOUT 断开、则不会再发生这种现象。

对于为何 FLTb 在电源输入后下降、是否有任何可能的解释?

测量波形

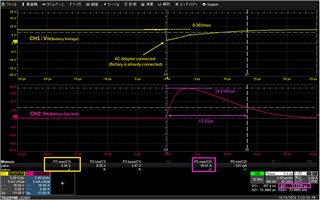

(1)在测量 SLOT1侧的 BQ25798 VBUS 端子电流时

(2)当测量 SLOT2侧的 BQ25798 VBUS 端子电流时

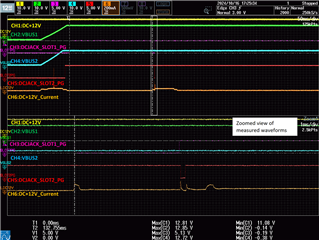

(3)测量直流插孔(DC12V)基极的电流时

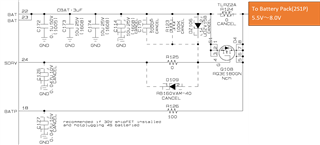

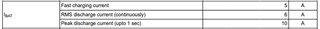

您过去查看过的电路配置、这会在输入源丢失的情况下断开电池与 BQ25798的 BAT 和 BATP 的连接、但在存在 VBUS 电源的情况下连接电池时、会从电池产生浪涌电流、并连接到 BQ25798的 BAT/BATP 端子。 (最大18.01A、13.53μs)

我们过去听说过、最大值被指定为10A、持续1秒、但是波形是否有任何问题?

我们将向您发送一份概述测量条件等的 PDF 报告 请检查它。

此致、

Kagawa

尊敬的 Kagawa:

电流形成浪涌、用于对连接到 BQ25798 VBUS、PMID、SYS 和 BAT 引脚的电容充电。

在输入侧、我怀疑 TPS25947 ILIM 钳位跳闸。 如果可能、我建议 使用第二个电阻器+串联 FET 将其设置为较高的启动时间、然后设置为较低的启动时间。

在输出侧、有一条通过 BATFET 体二极管到达 SYS 电容器的路径、然后通过高侧体二极管和电感器到达 PMID 二极管。 18A 尖峰持续13us 并非意外现象、也不违反10A 规范(持续1秒)。

此致、

Jeff

尊敬的 JEFF-SAN:

TPS259470A 的 RILM 电阻设置为560Ω、电子保险丝的 ILIM 调节为5.954A。 我们还通过在 ITIMER 引脚和 GND 之间安装一个0.1uF 电容器来测量波形。

但是、FLT 端子处于低电平、无法看到任何改善。

即使在电流波形中未看到反向电流、FLT 引脚变为低电平的原因未知。

如果 BQ25798的 VBUS 线和 TPS25947EVM 的 VOUT 断开、则不会再发生这种现象。

请告诉我、除了下面的波形、是否有任何其他引脚需要监测。

此外、对于电源输入后 FLTb 引脚为何会下降、您有什么想法吗? 我们认为不会导致过流。

测量波形

(1)在测量 SLOT1侧的 BQ25798 VBUS 端子电流时

(2)当测量 SLOT2侧的 BQ25798 VBUS 端子电流时

(3)测量直流插孔(DC12V)基极的电流时

此问题与以下主题相关

BQ25798:肖特基势垒二极管-电源管理论坛-电源管理- TI E2E 支持论坛

https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1392087/bq25798-schottky-barrier-diodes

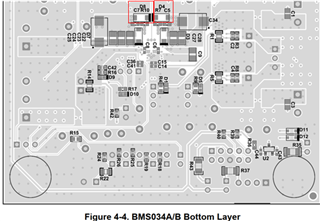

在本问题的前一版本中、当我询问肖特基势垒二极管的放置情况时、我被告知、这些二极管应尽可能靠近 SW 和接地、并且如果可能、不使用过孔。

但是、在 BQ25798EVM 中、相关的 D4和 D8通过过孔从电路板的背面连接、这与我们收到的答案不一致。

我们目前正在设计原图、不确定肖特基势垒二极管的放置应采用哪种方法。

建议将肖特基势垒二极管放置在什么位置?

此致、

Kagawa

尊敬的 Kagawa:

根据您发送的图表、充电器按预期工作。 我不希望布局发生任何变化。

至于二极管、EVM 上的二极管有助于在内部二极管发生故障时进行调试。 如果尝试使用更低 Vf 肖特基二极管来提高效率、则必须根据将该二极管放置在尽可能靠近 IC 引脚的位置、理想情况下与 IC 位于同一层、但如果不使用、则通过多个过孔连接。 否则、肖特基二极管的开启速度无法足够快、无法在开关死区时间内降低压降、也无法提高效率。

我建议创建另一个帖子、并向支持 TPS 部件的团队寻求帮助。

此致、

Jeff

尊敬的 JEFF-SAN:

此问题与以下帖子相关。

https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1041663/bq25798-ocp-and-ovp-timing?tisearch=e2e-sitesearch&keymatch=bq25798%2525252520ovp

上述文章回答了 OVP 和 OCP 检测之间的时间以及状态变化、但我想了解以下条件下的相同信息:

1.在 TS 线上的热敏电阻检测到温度变化后、BQ25798需要多长时间才能报告每个温度状态(TS HOT、TS WARM、TS COOL、TS COLD)?

2.从 BQ25798检测到电池插入或移除到状态寄存器(REG1D_REG2D2寄存器中的 VBAT_PRESENT_STAT Charger_Status_)需要多长时间?

3.从向 BQ25798的 Charger_Status_引脚施加有效输入电源到报告输入电源的电源正常状态(REG1B_REG0寄存器中的 PG_STAT)之间的时间是多少?

此致、

Kagawa

尊敬的 Kagawa:

关于1、如方框图所示、TS 功能是监控 TS 线路上电压的比较器梯形电路。 具有30ms 的抗尖峰脉冲功能、可防止抖动。

关于2、只要充电终止检测抗尖峰脉冲= 250ms、VBAT_PRESENT 就可能需要一段时间。

关于3、对于安装了多路复用器 FET 的 VAC2或禁用自动 D+/D-的 VAC1、ACDRVx 具有30ms 抗尖峰脉冲、 REGN 具有150ms 开启时间、电源不良检测具有另30ms 时间。 对于 D+/D-导通时的 VAC1、与上述相同、 并且至少加500ms 以及另加30ms、以便 D+/D-完成。

此致、

Jeff

尊敬的 JEFF-SAN:

从以下每个安全计时器的失效状态到相应状态位报告1 (安全计时器到期)的时间是多少?

涓流充电计时器(REG1E_REG3 Charger_Status_寄存器中的 TRICHG_TMR_STAT 位)

2.预充电计时器(REG1E_REG3 Charger_Status_寄存器中的 PRECHG_TMR_STAT 位)

3.快速充电计时器(REG1E_REG3 Charger_Status_寄存器中的 CHG_TMR_STAT 位)

此致、

Kagawa