主题中讨论的其他器件:TPS84250、

工具与软件:

你好。

它包含4个 TPS84250和4个 TPS84259。

四个 TPS84250输出被设定为+11.5V、这是因为我在 VOUT 和 VADJ (即引脚36)之间连接了一个133K 0.1%电阻器。

四个 TPS84259输出设置为-11.5V、因为我在 VOUT 和 VADJ (即引脚36)之间连接了一个133K 0.1%的电阻器。

对于所有情况、输入电压都是+24V、并且每个芯片的输入端都有一个+24V 的肖特基二极管。

我创建了本主题、用于查看 TPS84259的布局。 有四个电源在使用它、我对它进行了一次布局、我想进行验证、然后我将为其他三个进行一次复制。

即、我针对 TPS84250的布局已获得德州仪器(TI)工程师的"批准"、下面提供了此主题的链接。

e2e.ti.com/.../tps84250-layout-review

仅考虑铜层、PCB 的简化堆栈如下:

L1:顶部

L2:接地平面

L3:电源平面。 多个+11.5V 平面

L4:电源平面。 多个-11.5V 平面

L5:接地平面

L6:信号+接地

L7:接地平面

L8:底部

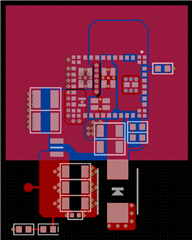

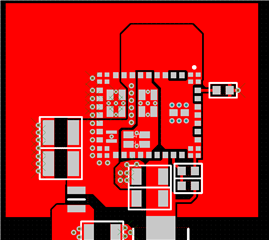

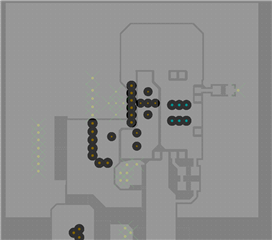

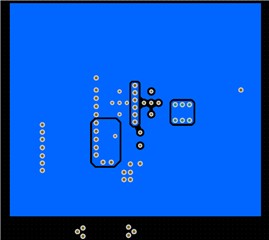

下面是我使用 TPS84259进行验证的布局图片。 下面未显示 L6是如何实现的、但在芯片区域的 L6中会有一个接地填充、类似于 L8底部、但放大了。

全视图:

L1、顶部:

L2、L5和 L7、接地平面:

L8、底部:

我的布局是否正常?

此致。