工具与软件:

尊敬的 Mike:

根据应用手册和上一篇文章、TABSET 和 TCDSET 应相等。 因为现在、我们将仅使用固定延迟选项。 建议不使用自适应延迟。

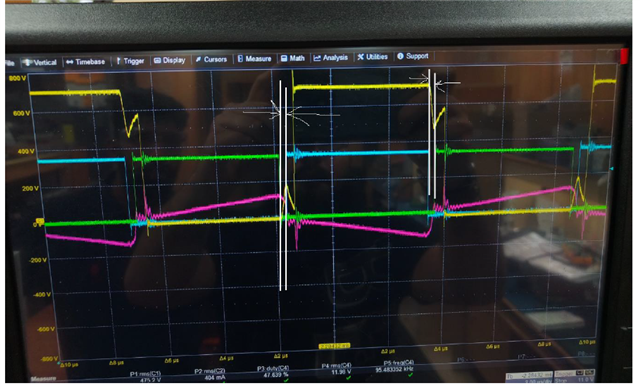

我设置了更多死区时间来了解问题。 D FET 正确关闭/关闭 ONN、与其中一个同步门(蓝色)相一致。 而 B 漏源波形(如果您观察到)会尝试关闭/关闭 ONN、但某种因素阻止了它。 应该尝试自适应延迟选项、还是应该继续使用固定延迟选项。 这与变压器的泄漏有关吗? 请提出建议。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 Mike:

根据应用手册和上一篇文章、TABSET 和 TCDSET 应相等。 因为现在、我们将仅使用固定延迟选项。 建议不使用自适应延迟。

我设置了更多死区时间来了解问题。 D FET 正确关闭/关闭 ONN、与其中一个同步门(蓝色)相一致。 而 B 漏源波形(如果您观察到)会尝试关闭/关闭 ONN、但某种因素阻止了它。 应该尝试自适应延迟选项、还是应该继续使用固定延迟选项。 这与变压器的泄漏有关吗? 请提出建议。

您好!

E 和 F 的导通延迟基于关断 A 和 B。 如果您使用的是自适应延迟、E 和 F 延迟将随 CS 信号而变化。

则必须包括 ADC 的绝对最大性能。 ADEL 和 ADEREF 将接地、或通过 VREF 和 ADEL ADEREF 引脚之间的分压器设置为接地。 如果您更改 RAB 和 RCD 的导通延迟而不更改 ADEL 和 ADELEF 上的电压、则不应更改 E 和 F 的导通延迟。 但是、如果您要以某种方式更改 ADEL 和 ADEREF 上的电压、您将更改延迟。 我会进行检查以确保没有调节 ADEL 和 ADEREF 处的电压来调节 TABSET、TCDSET 时序。 您应该只需要调整 RAC 和 RCD 电阻器。

您仍需要设置 A、B、C 和 D 的开启延迟才能删除您看到的原始问题。

此致、

您好!

OUT F 的导通延迟应基于 REF 设置的延迟和 OUT A 的关断

OUT E 的导通延迟应基于 REF 设置的延迟和 OUT B 的关断

如果 ADEL 和 ADELEF 都接地、那么我不会认为更改 RAB 和 RCD 会在 OUT E 和 OUT F 变为高电平时产生影响。

您是否在控制器的 OUT A、OUT B 以及 OUT E 和 OUT F 处验证了这一点?

我认为唯一能想到的可能是不同的。 如果您减小 OUT A 的接通延迟。 输出 D。 这将增加可实现的最大占空比。 OUT F 和 E 的行为将根据此发生变化。 但是、它们应该仍会根据 OUT A 和 OUT B 变为低电平而导通。 请注意、OUT E 和 OUT F 在 续流期间将较高。

此致、

我将在稍后分享一些测试图像。 我想了解几件事。

1.分享使用 SIC MOSFET 进行 PSFB 的数据。 目前在下一修订版原理图中,我参考东芝5KW 参考设计(5 KW 隔离式双向直流-直流转换器参考设计|东芝电子器件与存储公司|亚洲-英语 )

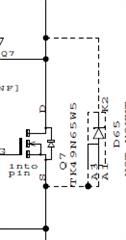

2.另外,为了加快初级 FET (SIC MOSFET)的关断速度,是否可以 分流 SiC 二极管以加快关断速度? 它会干扰 ZVS 或相关的东西吗? 图像如下所示

3、 如果按照 Excel 的要求需要匀场电感器,我们不使用匀场电感器? 后果是什么? 它是仅硬开关还是会干扰任何其他波形?

4.在初级侧的漏极到源极 FET 之间添加陶瓷电容器、如下所示。 这是在 CT 之后。 我们可以这样做吗?