工具与软件:

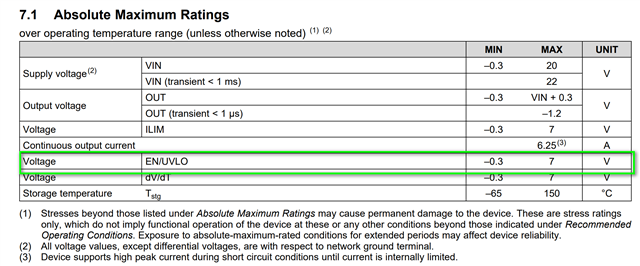

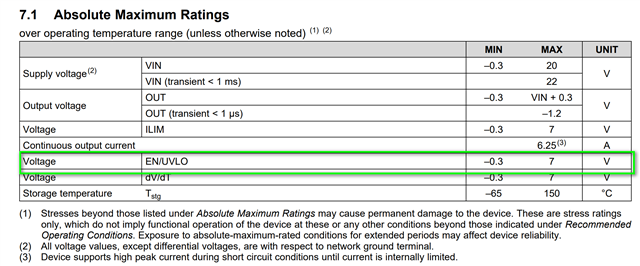

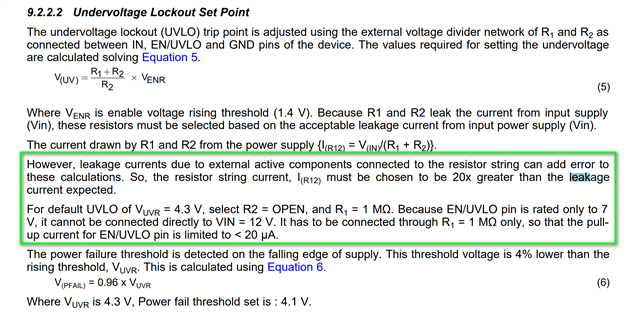

1、看手册要求EN μ A/UVLO 是有最高7V的电平要求

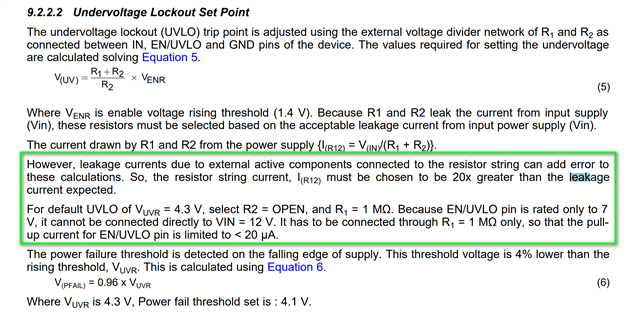

2 μ、但是看设置欠压保护的描述、貌似也可以超过7V、只要电流保证即可、下面的参考设计就是R1设置成1M即可?A

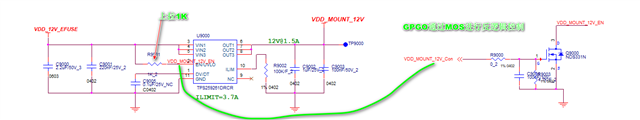

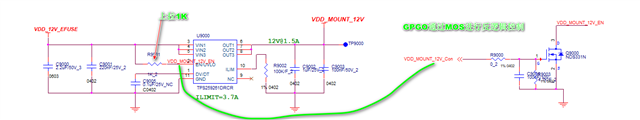

3、这个管脚的设置以哪个要求进行参考设计呢?如果以电流要求、电流最高要求多少呢、我们目前设计成下面的状况、发现也是OK的、帮忙看看这样设计是否存在风险

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

1、看手册要求EN μ A/UVLO 是有最高7V的电平要求

2 μ、但是看设置欠压保护的描述、貌似也可以超过7V、只要电流保证即可、下面的参考设计就是R1设置成1M即可?A

3、这个管脚的设置以哪个要求进行参考设计呢?如果以电流要求、电流最高要求多少呢、我们目前设计成下面的状况、发现也是OK的、帮忙看看这样设计是否存在风险

尊敬的 Dang Jinfa:

[报价 userid="574298" url="~/support/power-management-group/power-management/f/power-management-forum/1432745/tps25926-en-uvlo "]1、看手册要求EN μ A/UVLO 是有最高7V的电平要求

[报价]是的、 该引脚的电压不应高于7V。

Unknown 说:2、但是看设置欠压保护的描述、貌似也可以超过7V、只要电流保证即可、下面的参考设计就是R1设置成1M即可?

这里我们还有下拉电阻器、因此引脚上的电压不会超过7V。

Unknown 说:3、这个管脚的设置以哪个要求进行参考设计呢?如果以电流要求、电流最高要求多少呢、我们目前设计成下面的状况、发现也是OK的、帮忙看看这样设计是否存在风险

当 FET 关断时、这存在一些风险、EN 引脚将达到12V、超出最大限值。 您是否能够在 VIN 和 GND 之间使用电阻梯向 EN 引脚提供必要的电压。 您还可以连接 FET 以进行有源下拉。

此致、

Arush