请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS65910 工具与软件:

您好!

这是上一个问题的延续。 在阅读此帖子之前、请参阅相关主题帖。

我采取了使用上电延迟电路(CR 时间常数电路等)来减慢 VDDIO 上升的措施、使其处于数据表规格范围内。

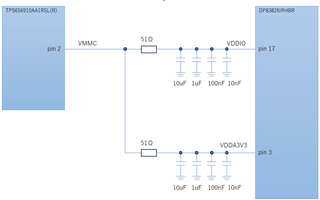

CR 时间常数电路(如下所示电路)满足电源规定的压摆率规定、但当 DP83826数据表第14页列出的消耗电流(MAX 55mA)流动时、51Ω 器件会出现较大的压降、VDDIO / VDDA3V3无法保持在3.3V。

如果您能建议任何其他措施、我将不胜感激。

谢谢!

Conor