Thread 中讨论的其他器件: LP8764-Q1

工具与软件:

尊敬的团队:

我的客户正在评估为 DAR821-Q1供电的 TPS6594-Q1和 LP8764-Q1。 关于上电顺序、当我们在第41至42页看到以下用户指南时、"6.3.8 TO_ACTIVE"和"图6-13. TO_ACTIVE Sequence"变量。

使用 TPS6594-Q1和 LP8764-Q1为 DRA821供电(修订版 A)

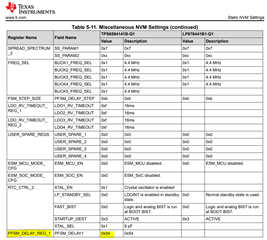

如 图6-13所示。 TO_ACTIVE 序列、描述了每个电源轨的总延迟。 该总延迟是否由 PFSM_DELAY_REG_1寄存器设置?

每个电源轨的这个总延迟是否由 TPS6594-Q1和 LP8764-Q1的哪个寄存器设置?

PFSM_DELAY_REG_1、PFSM_DELAY1 = 0x54设置什么?

此致、

二宫幸志