Other Parts Discussed in Thread: TPS7A20, TPS7A26

主题中讨论的其他器件: TPS7A26

工具与软件:

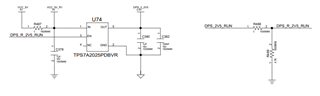

你好。 在本项目中、使用 TPS7A20构建电路。

连接到 TPS7A20的负载的电流消耗不超过10mA。

我正在尝试通过控制 FPGA 上的 VEN 来打开/关闭 TPS7A20输出。

当 VEN=0时、Vout 作为异常电压而不是0V (1.55V)输出

我想知道为什么会出现这种现象以及可以采取哪些解决办法。

由于内部安全策略、我无法提供完整电路。 因此、我附加了原理图中包含 TPS7A20的一部分。

连接的示波器捕捉显示了上电时电路板的状态。 (绿色= VIN (5V)、蓝色= VOUT (1.55V)、黄色= VEN)。

我怀疑问题可能是、尽管 VEN 为0、但输出显示为1.55V、这似乎是连接到输出端的 UVLO 电压。 请再回顾一下。

获取更多信息、当 VEN 为高电平时、输出为2.5V (正常运行)。