工具与软件:

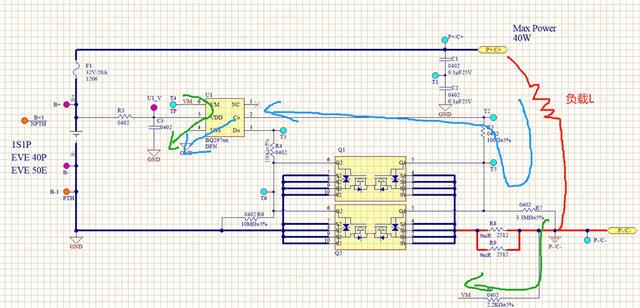

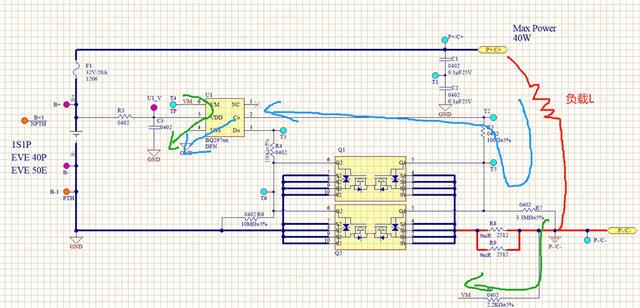

客户担心在过流保护和欠压保护下、下面两个电路环路中会有漏电流。

您能帮助对此进行评论吗?

蓝色一 (B+)P+--Load --P VSS --B-

绿色 P+--Load--P 负电压 VSS --B-?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

客户担心在过流保护和欠压保护下、下面两个电路环路中会有漏电流。

您能帮助对此进行评论吗?

蓝色一 (B+)P+--Load --P VSS --B-

绿色 P+--Load--P 负电压 VSS --B-?

Fabio 您好、

在欠压保护期间、V-引脚被电阻器 Rv 从内部上拉至 BAT ‘状态下的电流阱 Iv 未激活、如果存在任何"泄漏"、它将流向 BAT 而不是 VSS。

对于过流:

1)放电过流:V-和 VSS 引脚由一个用于检测负载的恒定电流吸收器(Iv)连接。

2)充电过流:V-和 Rv 与电流阱 Iv 之间的电阻 BAT-d 未连接。

中提供了更多详细信息 第8.4.3节"过放电状态"、第8.4.4节"放电过流状态"(放电过流、负载短路)和第8.4.5节"充电过流状态" 应用和实现部分。

此致、

Alexis

对于过流:

1)放电过流:V-和 VSS 引脚由一个用于检测负载的恒定电流吸收器(Iv)连接。

--- 所以在 OCD 的情况下,如果负载不移除,将会有泄漏。泄漏电流的范围可以称为"电流吸收器上的 V-",即8 24μA?的规格

2)它提到当 CO 和 DO 关闭时、仍然有0.5V 的阈值电压。 是否针对 CO 级别和 DO 级别相对于 VSS 测量了这个0.5V 阈值? 有关 VOL 的描述、请参阅第6.5节"直流特性-- FET 输出、DOUT 和 COUT"。

您好、Jian:

在查看过这篇文章之后、我意识到在提问和我的回复之间可能存在一些混淆。

澄清:

1)在检测到故障后、当 COUT 引脚关闭 CHG FET 时、COUT 引脚在内部被拉至 VSS。 这已正确显示在功能方框图中。

2) 2)不过、在测量 COUT 引脚上的电压时、由于 CHG FET 现在已关闭、COUT 引脚应相对于 V-/PACK-。

对此可能造成的任何混淆、我深表歉意。

此致、

Alexis