工具与软件:

您好!

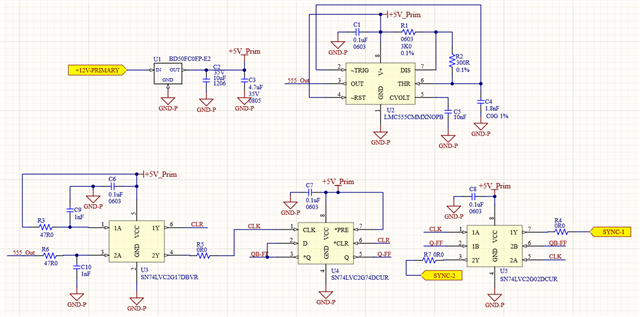

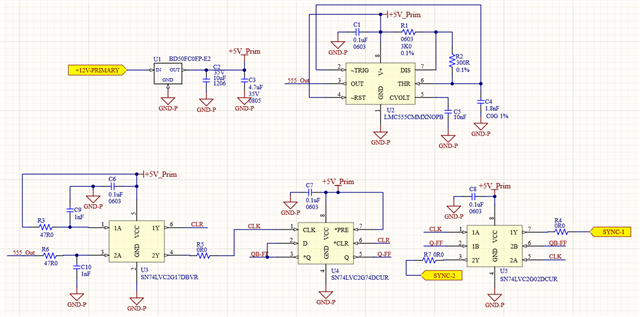

我将 设计一种四相交错 PFC。 我已经设计了它的2相版本。 在两相版本中、我使用了内部振荡器。 在四相版本中、我必须使用180度相移的外部同步信号。 我设计了一个555计时器和基于 D Flipflop 的电路来生成信号。 您能否查看连接的电路并查看我是否可以使用它来生成同步信号? 如果电路有问题、请建议进行任何更改。

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我将 设计一种四相交错 PFC。 我已经设计了它的2相版本。 在两相版本中、我使用了内部振荡器。 在四相版本中、我必须使用180度相移的外部同步信号。 我设计了一个555计时器和基于 D Flipflop 的电路来生成信号。 您能否查看连接的电路并查看我是否可以使用它来生成同步信号? 如果电路有问题、请建议进行任何更改。

谢谢。

您好、Zaka、

总体而言、您的同步电路看起来非常好。

我 建议进行以下修改:

1.将555_OUT 低的时间缩短至大约300ns 宽。 您希望 SYNC-x 脉冲尽可能窄、且不小于200ns。

2.使用上部施密特触发缓冲器(U3-1、6处)生成延时信号、而不是 CLR 信号。

在上电时无需清除 U4。 首先启动哪个 SYNC-x 输出无关紧要。。。 它与交错无关。

而是将"CLK"馈入 U3引脚1输入处的 RC (除了馈入 U4-1)。 将 R3和 C9值配置为~20ns 延时时间。

将 U3-6处的"CLR"输出更改为"CLK_DLY"、然后将 CLK_DLY 馈入 U5引脚1和5。

进入 NOR 输入的这种延时时间将允许 Q-FF 和 QB-FF 在 CLK_DLY 到达之前切换状态并达到稳定、从而使 SYNC-1和 SYNC-2无毛刺脉冲。

U4输出无竞态条件。

此致、

Ulrich