工具/软件:

尊敬的 Champ:

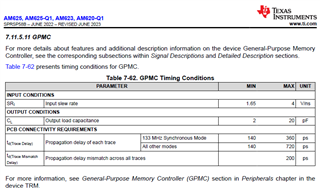

在 AM625数据手册 GPMC 时序条件表中、该表指示了 PCB 连接要求。

对于 td (布线延迟)、每个布线的传播延迟、对于133Mhz、最小140ps 和最大360ps。

对于 PCB、此特性是否为自身、堆叠和布局布线传播延迟需要在该范围内?

是否不能确定总布线长度产生的延迟、对吧?

下一个参数 td (布线不匹配 延迟)、最大值200ps、不匹配的定义是什么?

每个信号布线长度之间不匹配? 200ps 可能是1000mil 的布线长度差异。

我认为此处的失配不应该是布线长度差异。

PCB 布局布线等效传播延迟的特性是否基于其堆栈、布线宽度和参考层?

最后、GPMC 是否有布线长度限制?

Br、Rich