工具/软件:

尊敬的支持团队:

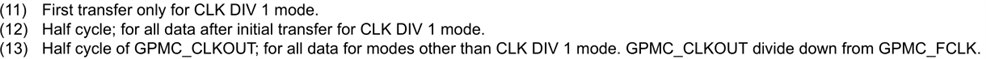

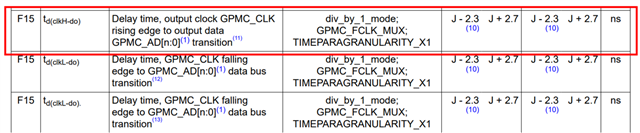

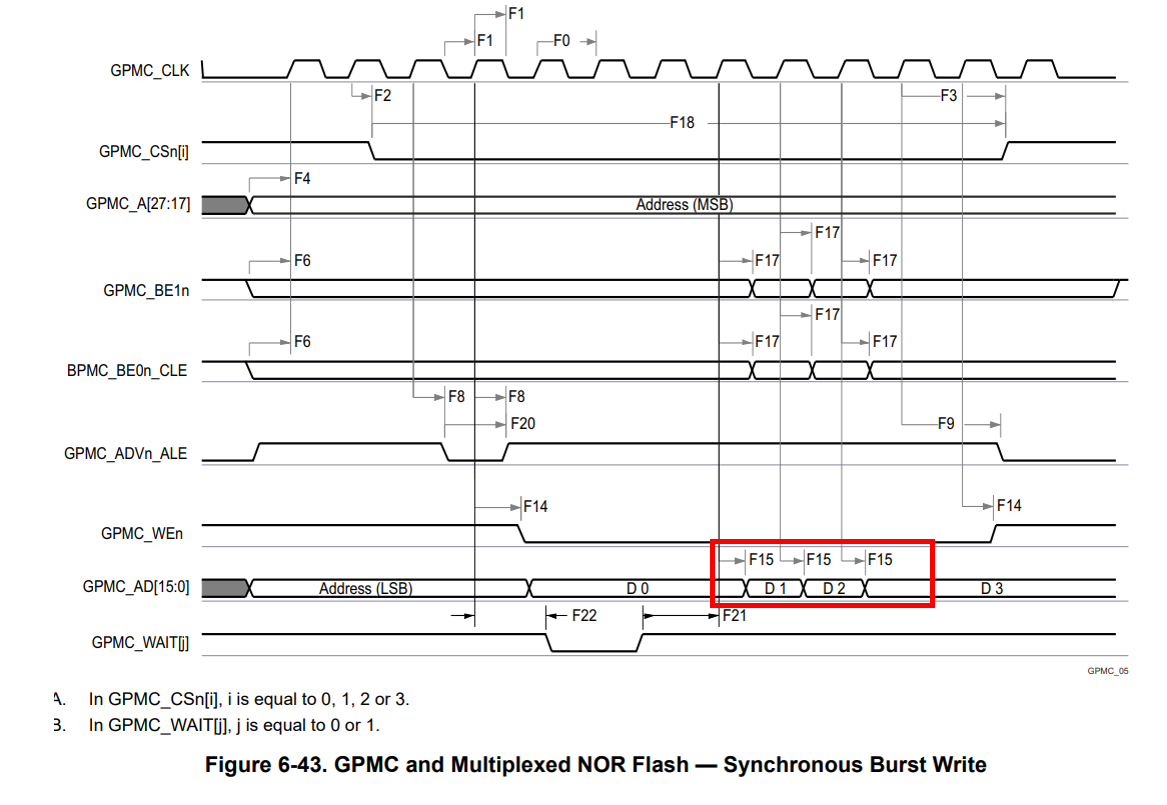

我想确认 AM6442数据表:表6-55。 GPMC 和 NOR 闪存开关特性-同步模式。

我的客户正在开发使用 AM6442的电路板、并尝试在 FPGA 中设置时序限制(设置、保持)。

在上述规范中、J = GPMC_CLK、因此在50MHz 时、该值为20ns。

在本例中、最小值为17.7ns、最大值为22.7ns、因此预期有效数据宽度是正确的 介于17.7ns 和22.7ns 之间 ?

与其他规格不同、该规格只指定转换时间、因此我来确认一下。

此致、

Kanae