主题中讨论的其他器件:SysConfig、

工具/软件:

我们正在新工程中验证 AM6232 + 4Gb DDR4、发现了 2 个问题:

1. 我们测试了 UDQS 和 DQ12、tDQS2DQ max 为 1.0398、高于 Creteria 0.17UI、tDQSCK 为–350.37ps、小于 Creteria –225ps

2. 我们测试了 LDQS 和 DQ6, tDQS2DQ max 为 3UI ,其中也比材料高。

是否有任何寄存器用于调整时序?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我们正在新工程中验证 AM6232 + 4Gb DDR4、发现了 2 个问题:

1. 我们测试了 UDQS 和 DQ12、tDQS2DQ max 为 1.0398、高于 Creteria 0.17UI、tDQSCK 为–350.37ps、小于 Creteria –225ps

2. 我们测试了 LDQS 和 DQ6, tDQS2DQ max 为 3UI ,其中也比材料高。

是否有任何寄存器用于调整时序?

您好 Kris、能否提供您正在使用的特定 DDR? 此外、您是否使用了 DDR 寄存器配置工具 https://dev.ti.com/sysconfig/?product=Processor_DDR_Config&device=AM62x 来为您的特定 DDR 和电路板配置 DDR 子系统? 如果是、请提供生成并在代码构建中使用的文件 (.dtsi 或.h 和.syscfg)。

此致、

James

您好、James

PFA、感谢一如既往的支持。

e2e.ti.com/.../0081.k3_2D00_am62x_2D00_ddr_2D00_config.dtsie2e.ti.com/.../0081.settings_5F00_info.syscfg

此致

Zekun

您使用的是 512Mbx8 还是 256Mbx16? 我假设您使用的是 x16 器件。 您使用的是哪种速度等级的器件?

您已设置 CL=17 和 CWL=12、但对于运行的工作频率、它应该为 CL=14(或 13)、CWL=11(或 9)。 对于 1600MTs、CA 奇偶校验延迟应为 4 个时钟。 如果您在 95°C 下工作、tREFI 需要 3900ns(当您更改工作温度时,工具会自动更改此值。 此外、我们在哪里得到 tRCD = 14.16ns。

可能网络上的数据表不适用。 请发布您正在使用的数据表。

此致、

James

e2e.ti.com/.../ISSI_2D00_43_2D00_46QR85120B_2D00_16256B_2D0008FF094E1F66FF66E34E09FF2800_1_2900_.pdf

我们使用 IS43QR16256B-083RBLI 256MB*16 型号、数据速度为 2400。

我将 SysConfig 的参数调整为 1600 数据速率、并将 syscfg 和 dtsi 文件匹配到以下 docx 文件、

但系统无法启动并在 uboot 中阻止、请帮助检查

e2e.ti.com/.../sysconfig_2D00_1600.docx

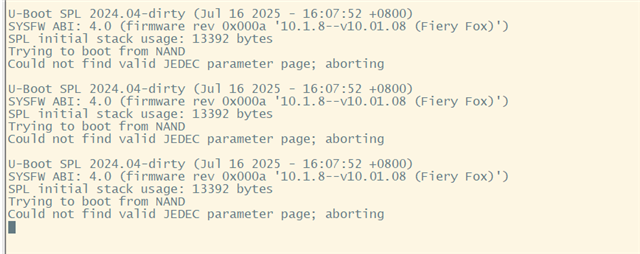

引导日志:

您是否可以尝试将附加的文件加载到 SysConfig DDR 工具中并使用生成的配置运行。 我注释掉了一些行、以减少变量的数量。

您是否还能发送有效的.dtsi 文件? 它是 SDK 中的默认文件吗?

此致、

James

您是否还能发送有效的.dtsi 文件? 它是 SDK 中的默认文件吗?

我附加了可 在以下 docx 文件中使用的 syscfg 和 dtsi 文件、请检查。 我根据 DDR4-2400 数据速度配置它,而不是 SDK 中的默认文件

您可以尝试使用随附的文件(DDR4-1600 配置)、但我更改了 CWL=11、并禁用了 CA 奇偶校验延迟

此致、

James

嗨、BERT、我不知道为什么 1600 配置不适合您。 我一直在比较这两种情况、我认为唯一会产生重大影响的是以下变化:

DDRSS.DDR4.config_dram_mr0_cl = 13;

DDRSS.DDR4.CONFIG_DRAM_Mr2_CWL = 9;

DDRSS.DDR4.CONFIG_DRAM_MR5_ca_par_lat =“4 个时钟“;

如果您可以逐个更改、回到 2400 配置中的配置、那么我可能能够解释正在发生的情况。

此致、

James

您好、James

正如您所预测的那样、 恢复 cl/cwL/ca_par_lat 值与 1600 配置的 2400 配置相同后 、 系统可以正常引导。

请帮助解释原因,这可能是硬件布局问题吗?

DDRSS.DDR4.config_dram_mr0_cl = 17;

DDRSS.DDR4.CONFIG_DRAM_Mr2_CWL = 12;

DDRSS.DDR4.CONFIG_DRAM_MR5_ca_par_lat =“5 个时钟;

您是否同时恢复了所有这些功能? 如果是、您能尝试逐一更改吗? 这将有助于缩小问题范围。 可以尝试以下组合:

DDRSS.DDR4.config_dram_mr0_cl = 13;

DDRSS.DDR4.CONFIG_DRAM_Mr2_CWL = 12;

DDRSS.DDR4.CONFIG_DRAM_MR5_ca_par_lat =“5 个时钟;

DDRSS.DDR4.config_dram_mr0_cl = 13;

DDRSS.DDR4.CONFIG_DRAM_Mr2_CWL = 9;

DDRSS.DDR4.CONFIG_DRAM_MR5_ca_par_lat =“5 个时钟;

此致、

James

您好 :James:

以下 组合 (CWL=12) 可以正常启动

DDRSS.DDR4.config_dram_mr0_cl = 13;

DDRSS.DDR4.CONFIG_DRAM_Mr2_CWL = 12;

DDRSS.DDR4.CONFIG_DRAM_MR5_ca_par_lat =“5 个时钟;

以下 组合 (cwl=9) 不起作用、将在 uboot 中阻止

DDRSS.DDR4.config_dram_mr0_cl = 13;

DDRSS.DDR4.CONFIG_DRAM_Mr2_CWL = 9;

DDRSS.DDR4.CONFIG_DRAM_MR5_ca_par_lat =“5 个时钟;

您好、James

我需要时间进行调查。 可能有一些与 ca_par 延迟相关的时序、这需要增加 cas 写入延迟、并且无法在工具中正确计算该延迟。 我来检查一下

好的、等待您的回答

您是否需要 CA 奇偶校验? 如果没有、您应该能够将其禁用。

实际上我们没有太多的 DDR 经验,你建议启用 CA 奇偶校验吗? 启用 CA 奇偶校验时还需要执行任何其他工作?

此外、我们想测试 写入 CRC 函数、请告诉我如何启用 CRC 函数、我在 SysConfig 工具中找不到任何相关信息

请确保使用正确的标志进行编译。 有关更多信息、请 访问:https://software-dl.ti.com/processor-sdk-linux/esd/AM62X/11_01_05_03/exports/docs/linux/Foundational_Components /U-Boot/UG-DDRSS.html

此致、

James

尊敬的 BERT:

启用 ECC 后、总可用 DDR 大小减小 1/9、约为 0x3900000。 DDR 总大小应为 0x1c700000。 因此、U-Boot 中至少有三个必须相应调整的位置。

首先是总内存大小。 在 U-Boot 器件树 arch/arm/dts/k3-am62x-sk-common.dtsi 中:

内存@80000000{

...

REG =<0x00000000 0x80000000 0x00000000 0x80000000 >;

您可能已经将其大小更改为 0x20000000。 但请现在将其更改为 0x1c700000。

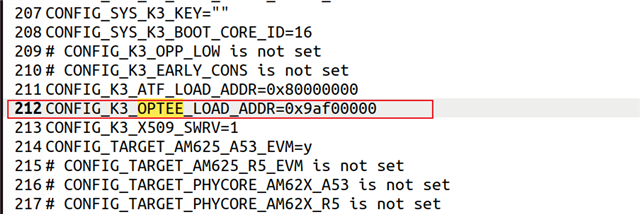

下一个是 OPTEE 加载地址。 它在 U-Boot 器件树 arch/arm/dts/k3-am62x-sk-common.dtsi 中定义:

SECURE_DDR:optee@9e800000{

REG =<0x00 0x9e800000 0x00 0x01800000>;/*对于 OP-TEE */

请将其位置 0x9e800000 更改为 0x9af00000。

最后、请在您的电路板 A53 defconfig 中按如下所示添加新的被测者加载地址。

CONFIG_K3_OPTEE_LOAD_ADDR=0x9af00000

嗨、Bin

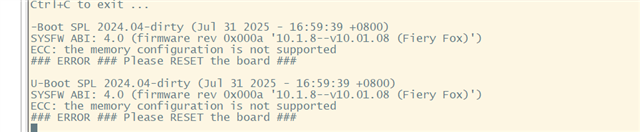

抱歉、延迟响应、仍然引导失败、正如您所说的完成、下面是引导日志

我的 DTS:

内存@80000000{

bootph-pre-ram;

device_type =“存储器“;

/* 512M RAM */

REG =<0x00000000 0x80000000 0x00000000 0x1c700000>;

};

SECURE_DDR:optee@9e800000{

REG =<0x00 0x9af00000 0x00 0x01800000>;/*对于 OP-TEE */

对齐=<0x1000>;

无映射;

};

尊敬的 BERT:

事实证明、ATF 和 OPTEE 包必须重新编译为新的 OPTEE 加载地址。

此外、一旦启用 ECC、当前 DM 固件位于 DDR 区域之外。 它也必须重新安置。 我会让你知道的变化的细节,一旦我想出.

BTY、

[引用 userid=“7730" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1537341/am623-ddr-delay-register-configuration/5950939首先是总内存大小。 在 U-Boot 器件树 arch/arm/dts/k3-am62x-sk-common.dtsi 中:

内存@80000000{

...

REG =<0x00000000 0x80000000 0x00000000 0x80000000 >;

您可能已经将其大小更改为 0x20000000。 但请现在将其更改为 0x1c700000。

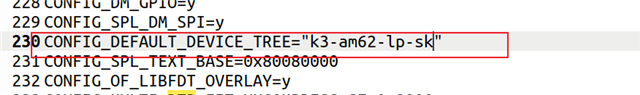

[/报价]必须在 arch/arm/dts/k3-am625-sk.dts 中完成此总存储器大小更改。 它会覆盖 k3-am62x-sk-common.dtsi 中定义的存储器@8000000 节点。

嗨、Bin

此外、一旦启用 ECC、当前 DM 固件位于 DDR 区域之外。 它也必须重新安置。 我会让你知道的变化的细节,一旦我想出.

好的、等待您的回答

必须在 arch/arm/dts/k3-am625-sk.dts 中完成此总存储器大小更改。 它会覆盖 k3-am62x-sk-common.dtsi 中定义的存储器@8000000 节点。

实际上、我们使用 k3-am62-lp-sk.dts、而不是 k3-am625-sk.dts

嗨、Zekun

好的

嗨、Bin

我已经创建了一个新的主题,让我们在其中讨论,非常感谢

e2e.ti.com/.../am623-system-can-t-boot-normally-when-open-ddr-ecc-function