Other Parts Discussed in Thread: TPS22965-Q1

器件型号: AM62A7

主题中讨论的其他器件: TPS22965-Q1

我参考了以下用户指南来检查电源连接和顺序。

TPS65931211-Q1 适用于 AM62A 的 PMIC 用户指南

www.ti.com/.../slvucm3.pdf

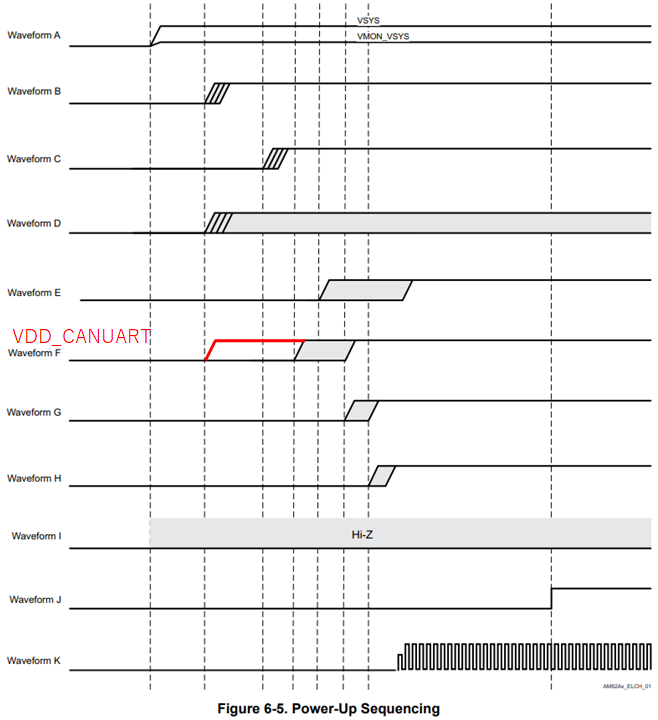

VDD_CANUART 和 1.8V IO 电源似乎不满足数据表中的上电序列要求。 VDD_CANUART 在 1.8V IO 电源之前上电。

是否允许 VDD_CANUART 在 1.8V IO 电源之前上电?

此致、

大辅