您好,TI:

我需要了解MPU配置和TI提供的不同选项方面的帮助。 我正在使用PSDK RTOS v 08.00。 具体来说,我想了解 在将某些内存区域配置为时,应选择哪些选项

- 内存顺序很严格

- 设备内存

- 正常内存

为此,我使用 CSL_ArmR5MpRegionCfg结构覆盖默认定义。 以下是一些默认的参考区域:

{

/* Region 0 configuration: complete 32 bit address space = 4Gbits */

.regionId = 0U,

.enable = 1U,

.baseAddr = 0x0U,

.size = CSL_ARM_R5_MPU_REGION_SIZE_4GB,

.subRegionEnable = CSL_ARM_R5_MPU_SUB_REGION_ENABLE_ALL,

.exeNeverControl = 1U,

.accessPermission = CSL_ARM_R5_ACC_PERM_PRIV_RD_WR,

.shareable = 1U,

.cacheable = (uint32_t)FALSE,

.cachePolicy = 0U,

.memAttr = 0U,

},

由于它们 之间存在某种程度的相互干扰,因此我感到困惑的字段包括:

- 可共享

- 可缓存

- cachepolicy

- MemAttr

我们来看一下代码示例。 此处,区域0具有以下选项:

- 可共享= 1

- 可缓存= 0

- cachepolicol =0 (根据CSL_ARM_R5_MPU.h,此字段仅在cacheable为true时有效,因此此处写入的值无效)

- MemAttr = 0 (CSL_ARM_R5_MEM_ATTR_GORIAL_ORITED_ORIGEO)

我的理解是,这会将这个特定的记忆区域宣布为“强烈顺序”,对吗? 保持缓存=0不变,我仍然在memAttr上有各种选项,这表明缓存将再次激活,尽管我明确取消它。 我所说的选项是:

/** \brief Memory type and cache policies: Strongly-ordered. */

#define CSL_ARM_R5_MEM_ATTR_STRONGLY_ORDERED ((uint32_t) 0x0U)

/** \brief Memory type and cache policies: Shareable. */

#define CSL_ARM_R5_MEM_ATTR_SHAREABLE ((uint32_t) 0x1U)

/** \brief Memory type and cache policies:

Outer and Inner write-through, no write-allocate. */

#define CSL_ARM_R5_MEM_ATTR_CACHED_WT_NO_WA ((uint32_t) 0x2U)

/** \brief Memory type and cache policies:

Outer and Inner write-back, no write-allocate. */

#define CSL_ARM_R5_MEM_ATTR_CACHED_WB_NO_WA ((uint32_t) 0x3U)

/** \brief Memory type and cache policies: Non cacheable. */

#define CSL_ARM_R5_MEM_ATTR_STRONGLY_NON_CACHED ((uint32_t) 0x4U)

/** \brief Memory type and cache policies:

Outer and Inner write-back, write-allocate. */

#define CSL_ARM_R5_MEM_ATTR_CACHED_WB_WA ((uint32_t) 0x5U)

/** \brief Memory type and cache policies: Non-shareable Device. */

#define CSL_ARM_R5_MEM_ATTR_NON_SHAREABLE ((uint32_t) 0x6U)

/** \brief This should be passed to configuration. */

#define CSL_ARM_R5_MEM_ATTR_MAX ((uint32_t) 0x7U)

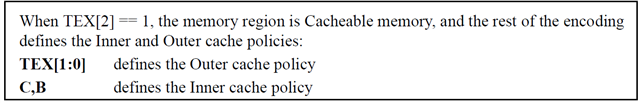

问题1:请详细说明不同的memAttr选项吗? 例如,当设置memAttr = CSL_ARM_R5_MEM_ATTR_cached_WB_WA同时将可缓存设置为0时,配置的确切内容是什么? 是否再次激活高速缓存? 这将导致质疑"可缓存"选项的目的。

问题2:当我要声明一些内存为强顺序/设备/正常时,是否需要将sharable设置为1? 通常可共享对内存有什么影响?

问题3:如果要将内存区域声明为“Device (设备)”或“Normal (正常)”内存,应该配置什么以及如何配置? 我是否必须使用 CSL_ARM_R5_MEM_ATTR_shareable?

感谢您的帮助和诚挚的问候,

费利克斯