主题中讨论的其他器件: SN65DSI83

你好

根据以下链接的内容、DSI 当前支持 TDA4VM 上的输出。

e2e.ti.com/.../tda4vm-tda4vm-dsi-support-on-linux

我们按照 TI 的说明修改内核相关设置。

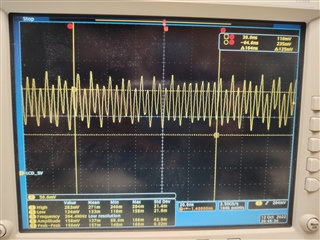

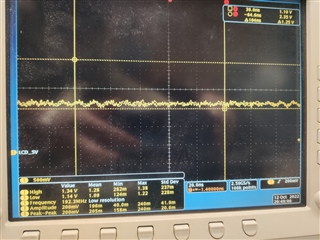

但我们没有测量任何 DSI 时钟(E10/E11 DSI_TXCLKN/P 引脚)波形输出。

我的环境如下:

===================================================================================================================================

硬件:[J721e SoC]--DSI->[SN65DSI83]---LVD-->[LVDS 面板1280x720]

操作系统:Linux SDK 8.4.11/Kernel 5.10.120

===================================================================================================================================

内核 DTS 设置如下所示

k3-j721e-main.dtsi

dsi0: dsi@48000000 {

compatible = "ti,j721e-dsi";

reg = <0x0 0x04800000 0x0 0x100000>, <0x0 0x04710000 0x0 0x100>;

clocks = <&k3_clks 150 1>, <&k3_clks 150 5>;

clock-names = "dsi_p_clk", "dsi_sys_clk";

resets = <&k3_reset 150 1>;

reset-names = "dsi_p_rst";

power-domains = <&k3_pds 150 TI_SCI_PD_EXCLUSIVE>;

interrupt-parent = <&gic500>;

interrupts = <GIC_SPI 600 IRQ_TYPE_LEVEL_HIGH>;

phys = <&dphy2>;

phy-names = "dphy";

#address-cells = <1>;

#size-cells = <0>;

dsi0_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

};

};

dphy2: phy@4480000 {

compatible = "ti,j721e-dphy", "cdns,dphy";

reg = <0x0 0x04480000 0x0 0x1100>;

clocks = <&k3_clks 296 1>, <&k3_clks 296 3>;

clock-names = "psm", "pll_ref";

#phy-cells = <0>;

power-domains = <&k3_pds 296 TI_SCI_PD_EXCLUSIVE>;

};

k3-j721e-test.dts

panel_disp0: panel_disp0@0 {

reg = <0 0 0x0 0x0>;

compatible = "panel-dpi";

power-supply = <®_backlight>;

enable-gpios = <&main_gpio0 117 GPIO_ACTIVE_HIGH>;

panel-timing {

clock-frequency = <75000000>;

hactive = <1280>;

vactive = <720>;

hback-porch = <140>;

hfront-porch = <14>;

vback-porch = <4>;

vfront-porch = <144>;

hsync-len = <2>;

vsync-len = <2>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

port {

panel_in: endpoint {

remote-endpoint = <&panel_bridge_out>;

};

};

};

&main_i2c3 {

pinctrl-names = "default";

pinctrl-0 = <&main_i2c3_pins_default>;

clock-frequency = <400000>;

status = "okay";

sn65dsi@2c {

compatible = "ti,sn65dsi83";

reg = <0x2c>;

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_bridge_in: endpoint {

remote-endpoint = <&dsi0_out>;

};

};

port@1 {

reg = <1>;

panel_bridge_out: endpoint {

remote-endpoint = <&panel_in>;

};

};

};

};

};

&dss_ports {

#address-cells = <1>;

#size-cells = <0>;

/* DP */

port@0 {

reg = <0>;

dpi0_out: endpoint {

remote-endpoint = <&dp0_in>;

};

};

/* DSI */

port@1 {

reg = <1>;

dpi1_out: endpoint {

remote-endpoint = <&dsi0_in>;

};

};

};

&mhdp {

pinctrl-names = "default";

pinctrl-0 = <&dp0_pins_default>;

};

&dp0_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dp0_in: endpoint {

remote-endpoint = <&dpi0_out>;

};

};

port@4 {

reg = <4>;

dp0_out: endpoint {

remote-endpoint = <&dp_connector_in>;

};

};

};

&dsi0 {

ports {

port@0 {

reg = <0>;

dsi0_out: endpoint {

remote-endpoint = <&panel_bridge_in>;

};

};

port@1 {

reg = <1>;

dsi0_in: endpoint {

remote-endpoint = <&dpi1_out>;

};

};

};

/*panel_disp0: panel_disp0@0 {

reg = <0 0 0x0 0x0>;

compatible = "lg,lh500wx1-sd03";

power-supply = <®_backlight>;

enable-gpios = <&main_gpio0 117 GPIO_ACTIVE_HIGH>;

port {

panel_in: endpoint {

remote-endpoint = <&panel_bridge_out>;

};

};

};*/

};

dmesg 日志作为附件文件

问题1:内核设置是否有任何问题?

Q2:如何使 DSI 时钟引脚输出频率信号?

谢谢。