您好!

我们将 AM3715的 MCSPI3_CLK 和 MCSPI3_SIMO 用于 FPGA 上传固件。

(未应用 MCSPI3_SOMI 和 MCSPI3_CSx、数据仅从 AM3715传输到 FPGA)

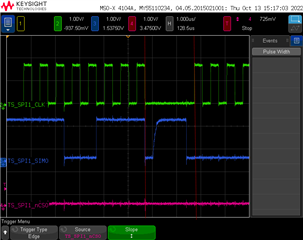

在数据传输期间、我们发现 一旦进入空闲模式(时钟停止)、MCSPI3_SIMO 似乎不再输出。

它看起来是高阻态、并通过 FPGA 内部上拉电阻(~40 kΩ)提升至半电压~0.8V。

此症状是否正确? 我们能否调整一些设置或代码、使 MCSPI3_SIMO 持续输出(H 或 L)为空闲模式、以解决 半电压症状?

BR、

Yume