器件型号:TDA3

您好!

我对交流时序的 SPI 有如下一些问题:

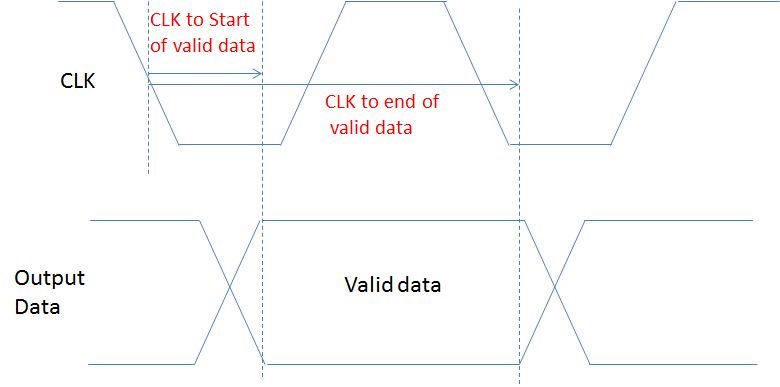

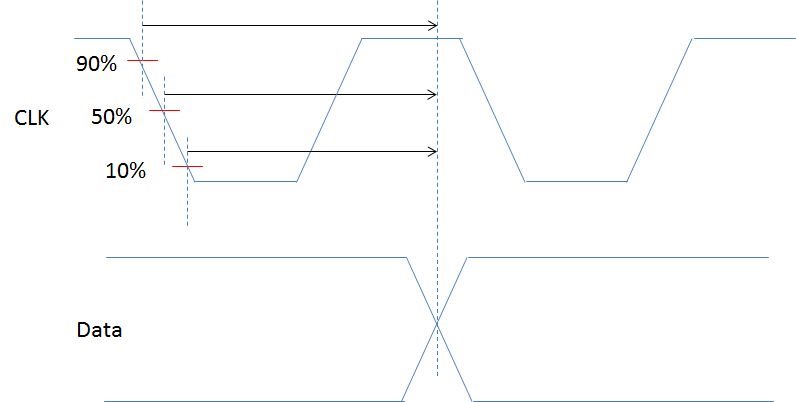

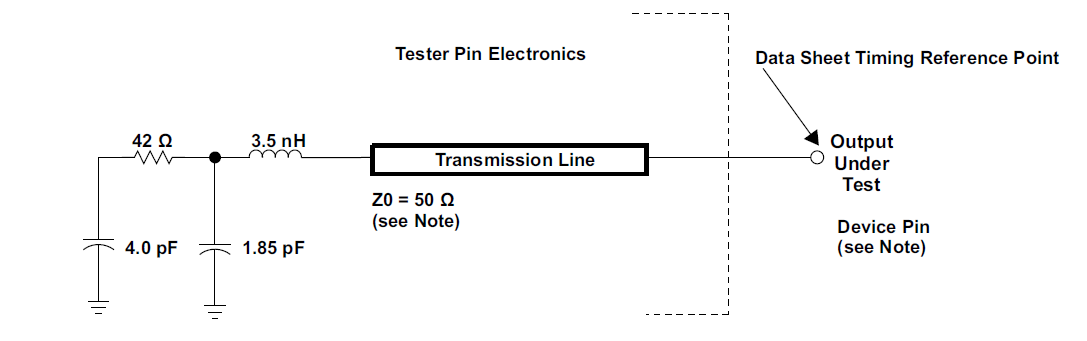

1) 1) 交流定时时间是否为时钟等信号振幅50%时的时间点?

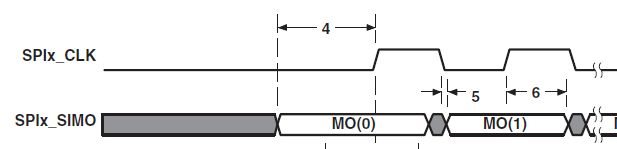

2) 2) 图7-25 McSPI 的 SS6 -从模式传输

SS6是如何定义数据信号的建立和保持时间的?

它定义了最小值和最大值。 如何从 DM 读取此数据的设置和保持时间?

3) 3) 图7-25 McSPI 的 SS7 -从模式传输

在 PHA = 1的情况下、第一个 SS6是 SS7? 但是、如果第一个 SS6是 SS7、则 SS7也是错误的数字。

此致、

肯什