主题中讨论的其他器件: LP873220、 TPS22965、 TPS22954

所有、

我对 AM5708 EVM 原理图"518202_DRA71x_DRA79x_TDA2Ex17_AM570x_EVM_OrCAD_PDF_Rev_C_24OCT2016.pdf"确实有几个问题。

-在 DDR 电源侧、为什么原理图中装配了 U72 (第8页)?

- DDR3模块由 LP8732x 的 BUCK1 (VDD_DDR)通过功率监控器感应电阻器加电

- AM5708 VDDS_DDR1由 U72从 VDD_DDR 生成的 VDD_DDR_CPU (通过功率监控器感应电阻器)供电

您熟悉 LP8733x (版本0x2D)和 LP8732x (版本0x20)的加电和断电排序(第7页- SNVU554-May17)–我们的 EVM 使用了0x2A 和0x2E 版本。

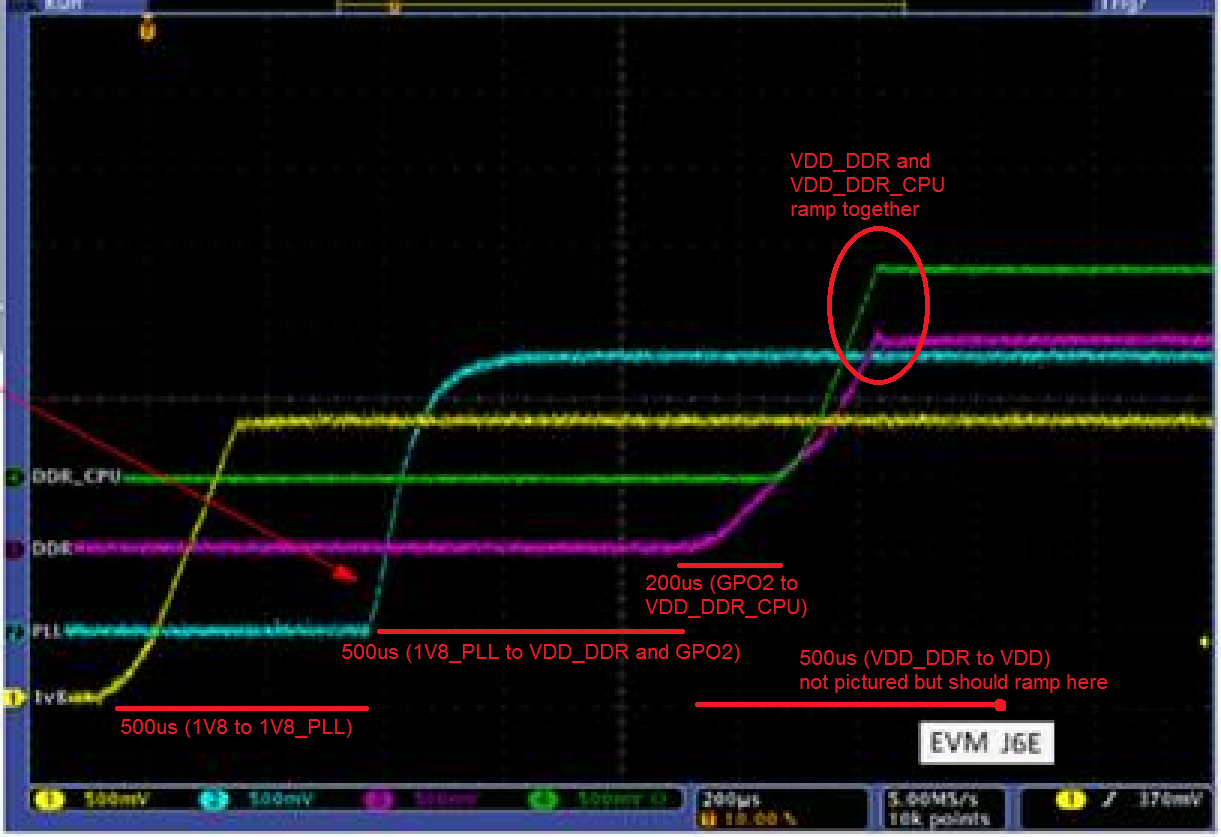

通过我们的原理图,VDD_DDR_CPU 和 VDD_DDR 之间存在0.8ms 的延迟,这是因为 U72导致 VDDS_DDR1比 PMIC 晚1.8ms,比 VDD (+1.15V)晚0.3ms:

- 0.0ms:PMIC 启用(随附 pdf 中的 EN 信号)

- 1.0ms:生成 VDD_DDR (LP873220_BUCK1)为 DDR3模块上电、同时通过 LP873220_GPO2启用 U72

- 1.5ms:生成 VDD (LP97332D_BUCK0)

-1.8ms:U72生成 VDD_DDR_CPU 以为 AM5708 VDDS_DDR1加电

这看起来与 AM570x 数据表(第153页- SPRS961A-Feb17页)形成对比、其中 VDDS_DDR1应在 VDD 之前出现–您怎么看?

最后但同样重要的是,查看原理图,还有一个开关(U122,第14页)用于控制 microSD 电源。

根据 microSD 规范,为了修改卡的工作电压,需要一个开/关周期。 在“SD mode”(SD 模式)的初始化阶段,访问已达到非活动状态的卡的情况也是如此。

由于根据应用要求,microSD 卡始终以3.3V 的电压加电并在“SPI 模式”中初始化,因此不需要再循环通电。 如果是、我可以避免使用开关并将 microSD 电源连接到 LP8733x 的 LDO0生成的 VDDSHV8–您对此有何感受?

请告诉我-这是一个紧急问题。

提前感谢您的友好支持。