主题中讨论的其他器件:TDA4VH

您好、TI 专家!

客户发现在 J784S4 SDK 9.0上、唤醒域 GPIO intr 到 A72 Linux 异常。

下面详细介绍了他们所执行的步骤。

首先、他们在"GPIO-keys"驱动器中添加了两个 GPIO、一个来自 MAIN_GPIO0、另一个来自 wkup_GPIO0。

下面提供了相应的补丁。

Date: Fri, 13 Oct 2023 18:38:23 +0800

Subject: [PATCH] add soc intr button

---

arch/arm64/boot/dts/ti/k3-j784s4-evm.dts | 38 ++++++++++++++++++++++++

1 file changed, 38 insertions(+)

diff --git a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

index 7db333b8fb04..c83b21c8a970 100644

--- a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -9,6 +9,7 @@

#include <dt-bindings/net/ti-dp83867.h>

#include <dt-bindings/gpio/gpio.h>

+#include <dt-bindings/input/input.h>

#include "k3-j784s4.dtsi"

/ {

@@ -28,6 +29,30 @@ aliases {

i2c0 = &main_i2c0;

};

+ gpio_keys: gpio-keys {

+ compatible = "gpio-keys";

+ autorepeat;

+ pinctrl-names = "default";

+

+#if 1 // works

+ pinctrl-0 = <&sw5_button_pins_default>;

+ sw5: switch-5 {

+ label = "GPIO Key USER1";

+ linux,code = <BTN_0>;

+ gpios = <&main_gpio0 0 GPIO_ACTIVE_LOW>;

+ };

+#endif

+

+#if 1 // not work

+ pinctrl-0 = <&sw6_button_pins_default>;

+ sw6: switch-6 {

+ label = "GPIO Key USER2";

+ linux,code = <BTN_1>;

+ gpios = <&wkup_gpio0 7 GPIO_ACTIVE_LOW>;

+ };

+#endif

+ };

+

memory@80000000 {

device_type = "memory";

/* 32G RAM */

@@ -345,6 +370,13 @@ J784S4_WKUP_IOPAD(0x000, PIN_OUTPUT, 6) /* (B34) MCU_OSPI0_RESET_OUT0 */

&wkup_pmx2 {

status = "okay";

+

+ sw6_button_pins_default: sw6-button-pins-default {

+ pinctrl-single,pins = <

+ J784S4_WKUP_IOPAD(0x0dc, PIN_INPUT, 7) /* (L36) WKUP_GPIO0_7 */ /* WKUP_PADCONFIG_55 */

+ >;

+ };

+

wkup_i2c0_pins_default: wkup_i2c0_pins_default {

pinctrl-single,pins = <

J784S4_WKUP_IOPAD(0x098, PIN_INPUT, 0) /* (N33) WKUP_I2C0_SCL */

@@ -521,6 +553,12 @@ ldoa4: ldo4 {

};

&main_pmx0 {

+ sw5_button_pins_default: sw5-button-pins-default {

+ pinctrl-single,pins = <

+ J784S4_IOPAD(0x000, PIN_INPUT, 7) /* (AN35) EXTINTn.GPIO0_0 */

+ >;

+ };

+

main_cpsw2g_pins_default: main-cpsw2g-pins-default {

pinctrl-single,pins = <

J784S4_IOPAD(0x0b8, PIN_INPUT, 6) /* (AC34) MCASP1_ACLKX.RGMII1_RD0 */

--

2.34.1

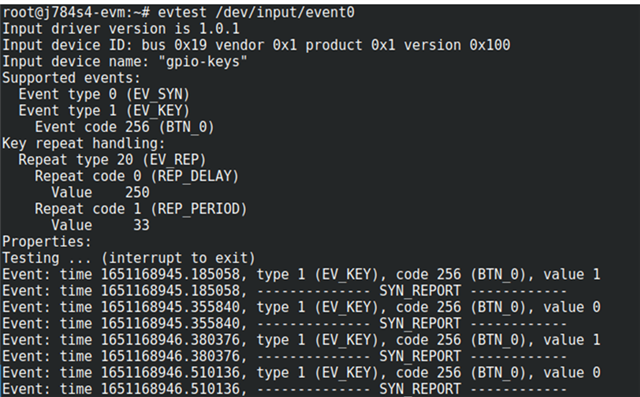

然后、客户使用 Evtest (这是一种测试 GPIO intr 输入事件的工具)来测试主域 GPIO 和唤醒域 GPIO。

对于主域 GPIO 的结果、结果为正常结果、如下所示、 当 在 J784S4 EVM 上按下"SOC_INT1"按钮时、Evtest 可报告不同的状态。

但是、 当按下或释放 EVM 上的"SOC_INT2"按钮时、唤醒域 GPIO 的 Evtest 报告会异常。

BTW、在 J721e EVM 上、还有两个 GPIO_keys 驱动程序的 GPIO、它们的中断均由客户正常验证、仅 TDA4VH 发生此问题。

您能提供一些关于这个问题的建议吗?

非常感谢!

凯文