工具与软件:

尊敬的 TI:

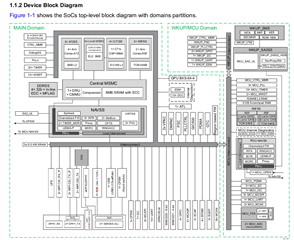

目前 TDA4上的 PCIe2_DAT0存在问题。 我们将使用 ti-uboot-2023.04来使 TDA4进入 u-boot 级、然后加载并启动 MCU2-0的固件。

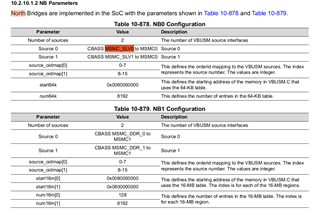

PCIe 模块索引2配置为通过 PCIe2_DAT0区域访问具有 TDA4的另一个电路板的存储器。

问题是、我无法从 MCU2-0访问 PCIe2_DAT0区域。 下面总结了我到目前为止所做的尝试:

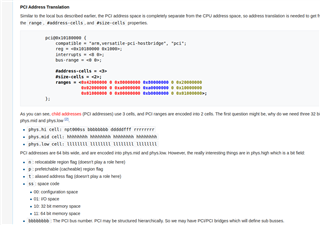

1. PCIe2_DAT0存储器位于48位地址空间内。 (0x4400000000)

MCU2-0的 RAT 单元配置为将此存储器区域(0x4400000000)映射到 ARMSS_RAT_Region2地址范围(0x10000000)

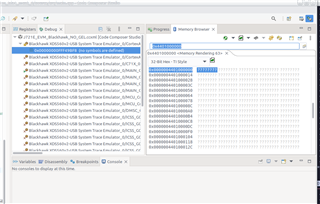

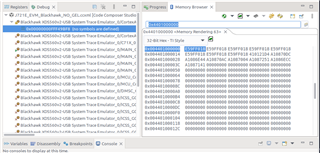

我将 CCS 连接到 MCU2-0、并使用内存浏览器从映射的存储器区域(0x10000000)中读取。

结果:我得到"?" 在"Memory Browser"视图中、看起来 TDA4已崩溃。

CCS 输出:MAIN_Cortex_R5_0_0:错误:(错误-1170 @ 0x0)无法访问 DAP。 重置设备、然后重试此操作。 如果错误仍然存在、请确认配置、对电路板进行下电上电、并/或尝试更可靠的 JTAG 设置(例如、降低 TCLK)。 (仿真软件包20.0.0.3178)

MAIN_Cortex_R5_0_0:尝试20次后无法确定目标状态

MAIN_Cortex_R5_0_0:在断开连接之前无法从目标移除调试状态。 程序存储器中可能仍嵌入了断点操作码。 建议您在连接和重新加载程序之前重置仿真器、然后再继续调试

2.尝试避免任何 RAT 配置问题、并使用 A72内核窥探 PCIe2_DAT0区域:

我将 CCS 连接到 a72、并使用内存浏览器从内存区域0x4400000000中读取。

它只是显示"?" (无法从该地址读取)但这次 TDA4不会像从 R5那样崩溃。

注意:"Memory View"设置为"CPU Memory View"。

3、和2相同、但这次我把 Memory Browser 的"Memory"视图设置为"Physical Memory View"。

现在我可以看到来自另一个板的数据。 (工作正常!)

对我来说、得出的结论是 PCI 配置/访问一般都可以正常工作。 但访问 PCIe2_DAT0存在一个一般问题。

您能在此处帮助我吗? 我们的最终目标是从 MCU2-0访问它。

谢谢、此致、

Thomas