请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM625-Q1 工具与软件:

嗨、团队:

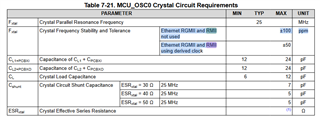

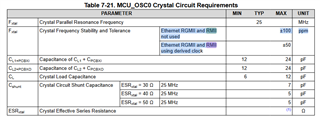

如果它们使用50MHz 时钟 RMII 和来自 AM625x 的输出时钟、则连接到 ETH PHY。 还可以将晶体的精度降低到100ppm 吗?

不确定这是否在字"派生的"时钟中被排除。

我会假设+/-100ppm 足够好。 请您确认吗?

谢谢

Jens

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

嗨、团队:

如果它们使用50MHz 时钟 RMII 和来自 AM625x 的输出时钟、则连接到 ETH PHY。 还可以将晶体的精度降低到100ppm 吗?

不确定这是否在字"派生的"时钟中被排除。

我会假设+/-100ppm 足够好。 请您确认吗?

谢谢

Jens

你(们)好

负载开关的规格。 其中规定"器件在 RGMII/RMII 模式下可耐受100ppm 晶振、..."

我们计划使用 PHY 的 RMII-clkmode。 在此模式下、外部50 MHz REF_CLK 用于为整个 PHY 计时。

我可以假设需要为 MAC 和 PHY 计时。 运行、直到该时钟不存在 FIFO 溢出等危险。

您能否说明在上述条件下+-100ppm 是否足够好?

此致

Friedrich