Other Parts Discussed in Thread: CDCE913

大家好!

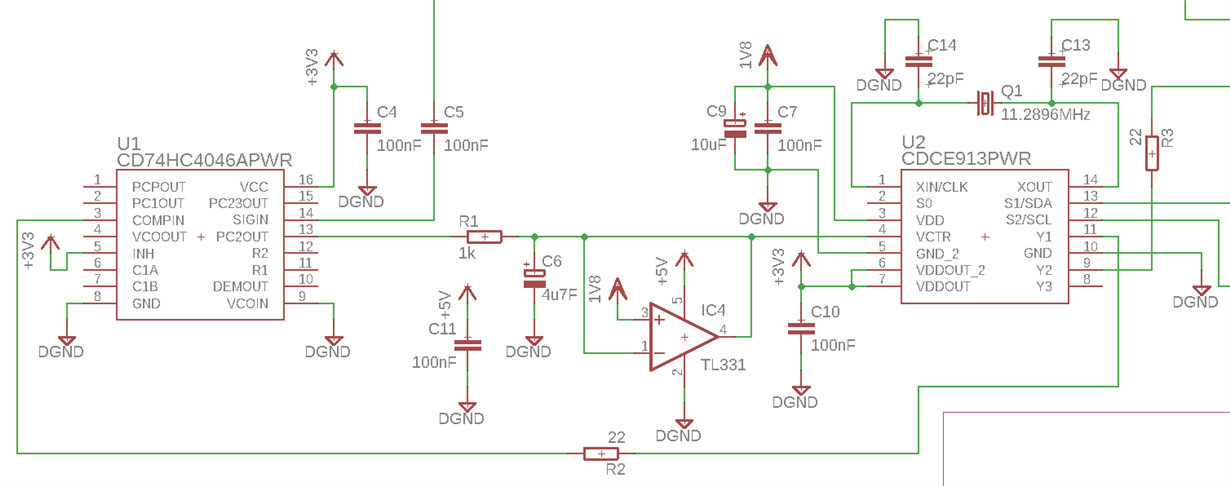

我正在尝试实施应用手册 SCAA088 来从 I2S 源(从 CD 播放器)生成主时钟。 但是、由于 PLL 未锁定、我在使其工作时遇到了一些问题(因此输出可以自由运行、输入源不在灌电流中)。 这是我的原理图:

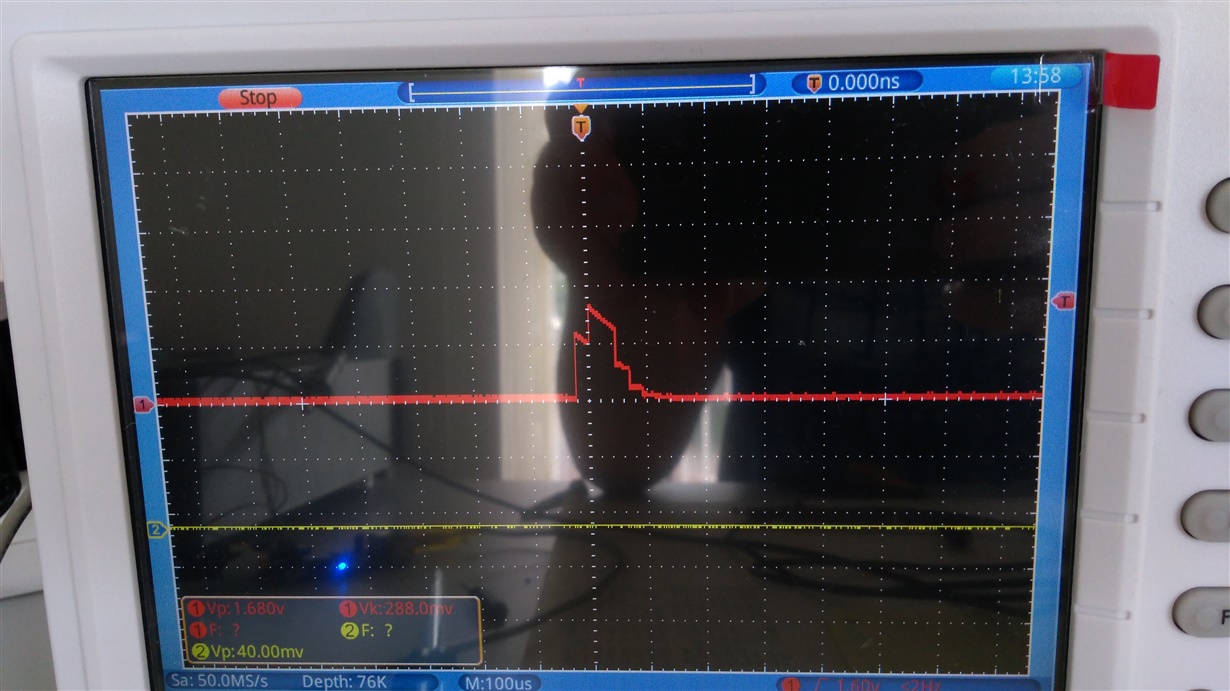

我已将输出分频器正确设置为所需的值(Y1输出44.1kHz 的时钟、Y2为晶振频率的一半)、CDCE913配置为在 VCXO 模式下运行。 但相位比较器的信号似乎未正确到达 CDCE913。 (它是平坦的零)。 拆下 RC 滤波器时、这就是我在示波器上看到的结果:

然而、PLL 锁定仍然没有区别。。。 有人有一些指示我尝试的吗?