主题中讨论的其他器件: AFE7950、 LMK04832

大家好、

我想向您确认、连接器 J14上向 AFE7950EVM 提供的外部时钟(例如163.68 MHz)如何分布在整个评估板上。

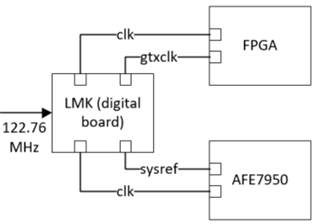

我知道 AFE7950系统时钟通道是必要的(例如、将从中得出 ADC 和 DAC 采样率)、但还有一个 LMK 可发送多个输出、其中一些输出将流向 FPGA (在本设置中、FPGA 连接到 AFE 评估板。 模块)。

LMK 是将外部时钟作为输入、然后向 AFE 和 FPGA 提供所有必要的时钟输出、还是在评估板上发生了任何额外的时钟信号分离?

此外、考虑到用户提供了专用的 LMK 器件、那么在独立模式下是否将同样的时钟分配应用于 AFE7950器件(没有附带额外 LMK 和其他元件的评估板)?

此致、

Željko μ A