Thread 中讨论的其他器件:AFE7900、 AFE7950EVM、AFE7950

工具与软件:

大家好!

我目前正在使用 ZCU102电路板和 AFE7900实施一个项目。 我的目标是绕过 FTDI、直接将 SPI 命令从 FPGA 写入 AFE7900和 LMK 芯片。

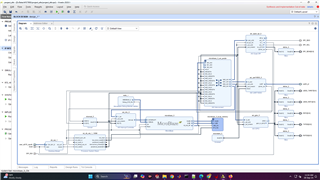

我一直按照 sba412a 文档中的说明操作、并成功在 Vivado 中创建了块设计。 但是、在为方框图的输出选择正确的 FPGA 引脚编号时、我遇到了一些困惑。

具体问题:

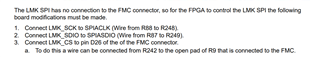

在本文档的第10节中、讨论了对 AFE79xxEVM 电路板的修改。 它提到了 LMK 片选的 SPI 线、与 FMC 连接器的引脚 D26相关。 原理图中将 D26称为 SPIASDO_FMC。

我是否应该将 D26引脚用于 LMK 的芯片选择、或者文档中是否错误地识别了该引脚? 如何正确地将 AFE7900和 LMK 的 SPI 线路(MOSI、MISO、SCLK、CS)映射到 FPGA 引脚?

第11节- AXI GPIO 配置:该文档还讨论了如何配置 AXI GPIO、但我不清楚如何正确地将这些引脚映射到 FPGA 的物理 I/O 引脚以进行 SPI 通信。