主题中讨论的其他器件: SN74LVC1G79、 TDC7201

工具/软件:

背景:

我尝试使用 TDC7200 以高分辨率测量时钟周期。 为了测试这是否可行、我用 mikroe 上的 TDC Click dev 板与 FTDI FT4222 进行对话。

为了测量周期、我使用 SN74LVC1G79 将触发信号锁存到目标时钟频率。 近似原理图如下所示:

问题:

如果我做了几个样本、则会返回随机不正确的数据、或者 TDC 将丢失 STOP 信号、否则数据将完全正确。 配置示例和测量~5kHz 输入频率的 5 个样本。 此处测量值 1 缺少停止信号、测量值 2 完全不正确、但 3-5 是预期值:

2025-06-25T20:12:38.369243Z INFO tdc720x: CONFIG1: Configuration1Register { force_calibration: false, parity_enable: false, trigger_edge: RISING, stop_edge: FALLING, start_edge: RISING, measurement_mode: Mode2, start_measurement: false }

2025-06-25T20:12:38.369896Z INFO tdc720x: CONFIG2: Configuration2Register { calibration_periods: Calibrate10ClockPeriods, number_of_averaging_cycles: Average1Cycles, number_of_stop_signals: One }

2025-06-25T20:12:38.370759Z INFO tdc720x: INT_MASK: InterruptMaskRegister { reserved: 0, clock_counter_overflow_mask: true, coarse_counter_overflow_mask: true, new_measurement_mask: true }

2025-06-25T20:12:38.373362Z INFO tdc720x: STOP Mask: 10

2025-06-25T20:12:38.374296Z INFO tdc720x: Clock overflow: 65535

2025-06-25T20:12:38.375046Z INFO tdc720x: Coarse overflow: 35

---------------------- Measurement 1 ----------------------

2025-06-25T20:12:38.877986Z INFO tdc720x: Timeout

---------------------- Measurement 2 ----------------------

2025-06-25T20:12:38.886500Z INFO tdc720x::tdc720x: INT_STATUS: InterruptStatusRegister { reserved: 0, measurement_completed: true, measurement_started: true, clock_counter_overflow: false, coarse_counter_overflow: false, new_measurement: true }

2025-06-25T20:12:38.889593Z INFO tdc720x::tdc720x: TIME1: TimeRegister { parity: false, measurement: 3072980 }

2025-06-25T20:12:38.890094Z INFO tdc720x::tdc720x: TIME2: TimeRegister { parity: false, measurement: 299 }

2025-06-25T20:12:38.890341Z INFO tdc720x::tdc720x: CLOCK1: ClockCountRegister { parity: 0, reserved: 0, measurement: 1600 }

2025-06-25T20:12:38.891628Z INFO tdc720x: 383.31474386169594 μs

2025-06-25T20:12:38.893052Z INFO tdc720x: 2.608822165110379 KHz

---------------------- Measurement 3 ----------------------

2025-06-25T20:12:38.901961Z INFO tdc720x::tdc720x: INT_STATUS: InterruptStatusRegister { reserved: 0, measurement_completed: true, measurement_started: true, clock_counter_overflow: false, coarse_counter_overflow: false, new_measurement: true }

2025-06-25T20:12:38.903341Z INFO tdc720x::tdc720x: TIME1: TimeRegister { parity: false, measurement: 1517 }

2025-06-25T20:12:38.903664Z INFO tdc720x::tdc720x: TIME2: TimeRegister { parity: false, measurement: 1477 }

2025-06-25T20:12:38.903931Z INFO tdc720x::tdc720x: CLOCK1: ClockCountRegister { parity: 0, reserved: 0, measurement: 1600 }

2025-06-25T20:12:38.904269Z INFO tdc720x: 200.0023852432948 μs

2025-06-25T20:12:38.904732Z INFO tdc720x: 4.999940369628795 KHz

---------------------- Measurement 4 ----------------------

2025-06-25T20:12:38.912598Z INFO tdc720x::tdc720x: INT_STATUS: InterruptStatusRegister { reserved: 0, measurement_completed: true, measurement_started: true, clock_counter_overflow: false, coarse_counter_overflow: false, new_measurement: true }

2025-06-25T20:12:38.913931Z INFO tdc720x::tdc720x: TIME1: TimeRegister { parity: false, measurement: 781 }

2025-06-25T20:12:38.914333Z INFO tdc720x::tdc720x: TIME2: TimeRegister { parity: false, measurement: 746 }

2025-06-25T20:12:38.914560Z INFO tdc720x::tdc720x: CLOCK1: ClockCountRegister { parity: 0, reserved: 0, measurement: 1600 }

2025-06-25T20:12:38.914994Z INFO tdc720x: 200.0020880840006 μs

2025-06-25T20:12:38.915555Z INFO tdc720x: 4.999947798444991 KHz

---------------------- Measurement 5 ----------------------

2025-06-25T20:12:38.921170Z INFO tdc720x::tdc720x: INT_STATUS: InterruptStatusRegister { reserved: 0, measurement_completed: true, measurement_started: true, clock_counter_overflow: false, coarse_counter_overflow: false, new_measurement: true }

2025-06-25T20:12:38.922392Z INFO tdc720x::tdc720x: TIME1: TimeRegister { parity: false, measurement: 552 }

2025-06-25T20:12:38.922830Z INFO tdc720x::tdc720x: TIME2: TimeRegister { parity: false, measurement: 516 }

2025-06-25T20:12:38.923225Z INFO tdc720x::tdc720x: CLOCK1: ClockCountRegister { parity: 0, reserved: 0, measurement: 1600 }

2025-06-25T20:12:38.923519Z INFO tdc720x: 200.0021471742127 μs

2025-06-25T20:12:38.923920Z INFO tdc720x: 4.999946321220971 KHz

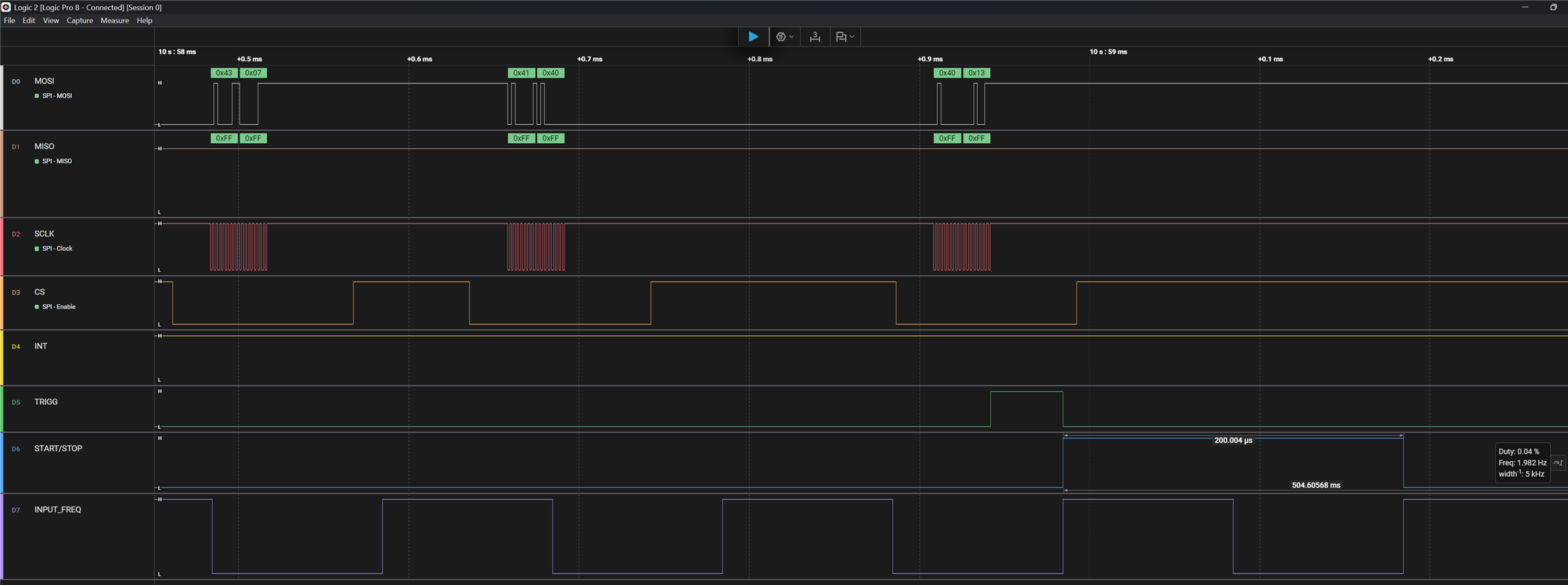

样本 1(错过的停止):

请注意、INT 在脉冲后不会变为低电平

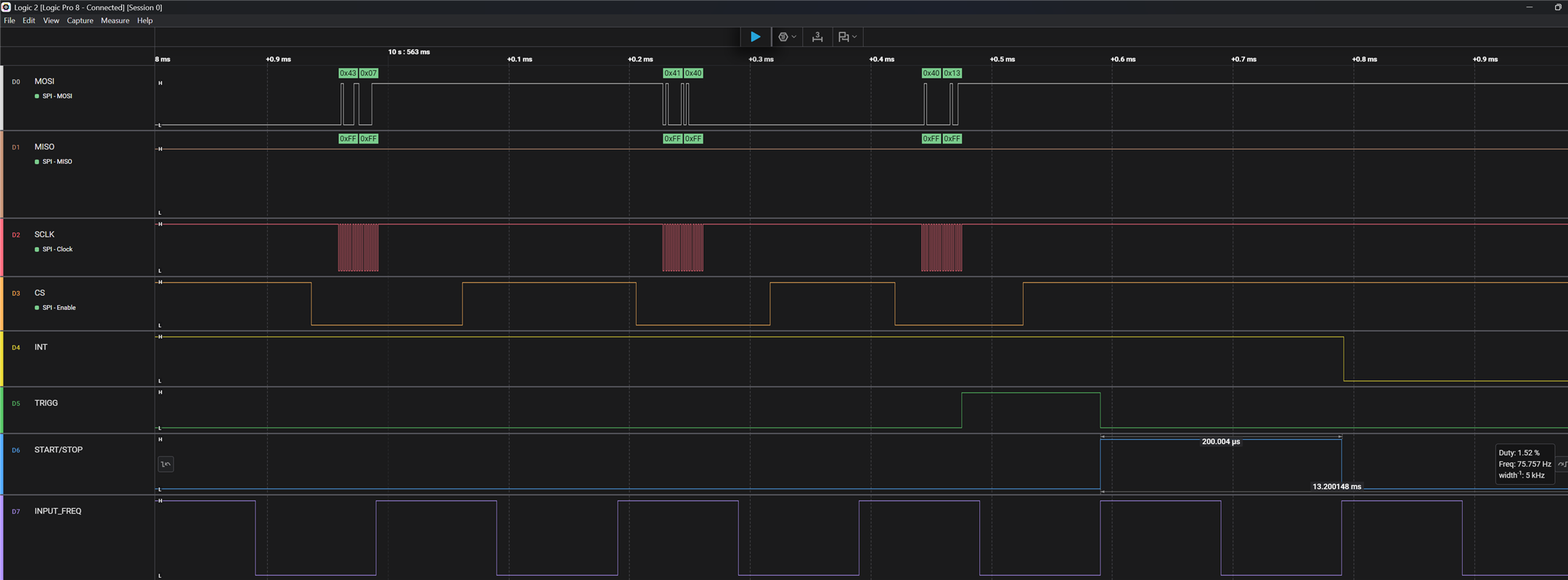

示例 2(错误数据):

请注意、脉冲仍是预期的 200us

和数据读数:

您可以看到 Time1 是前 3 个字节 0x2EE3D4 == 3072980

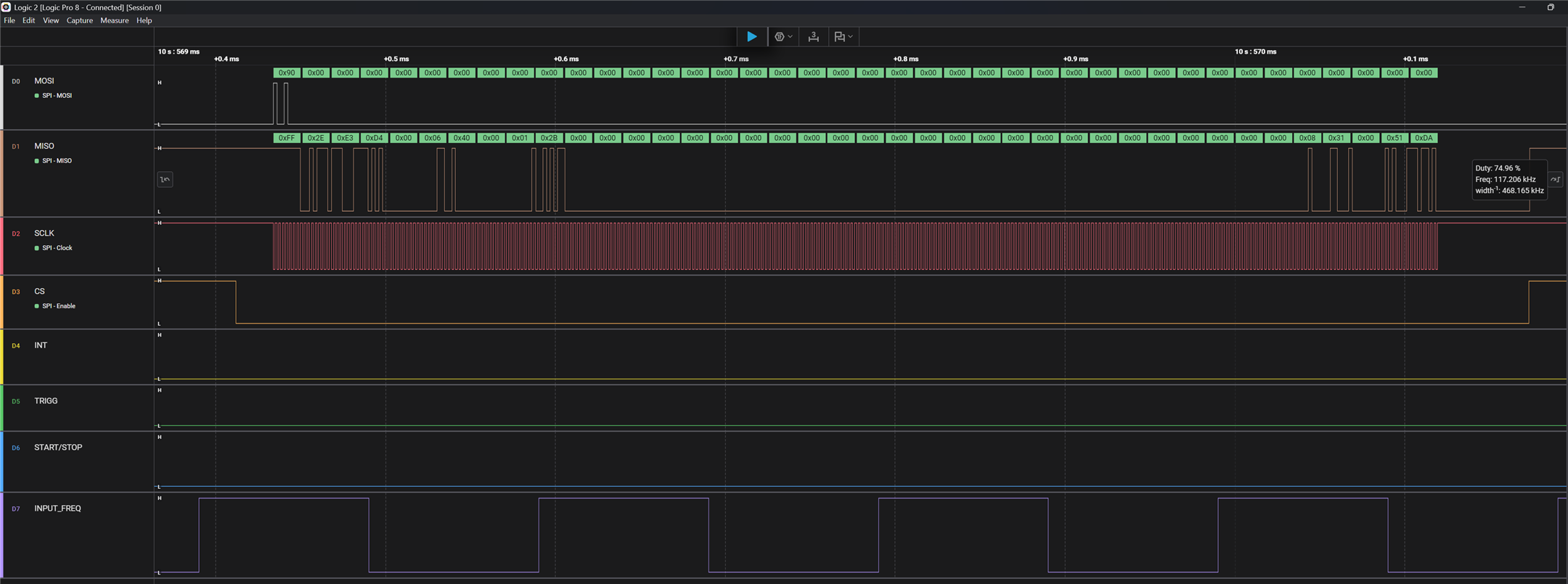

样本 3(正确的数据,4 和 5 的数据相同):

和数据读数:

问题:

-为什么 TDC 缺少这些止动边? 无论中断引脚 是否检测到停止边沿、是否应该在~8ms 后由于溢出而变为低电平(实际上,我在 500ms 后会有超时)? 它清楚地看到了开始沿、因为触发器引脚在上升沿之后不久变为低电平。

-启动和停止引脚连接在一起是否有某种问题?

-为什么 TDC 有时会返回错误的数据? 3072980 不应该导致 35 的课程计数器过滤器溢出并引发中断吗?

-当我将目标频率提高到 25KHz(40us 周期)时,每个停止边都会丢失(但在 8ms 时仍然没有溢出)。 这应该完全符合 TDC 的规格吗?