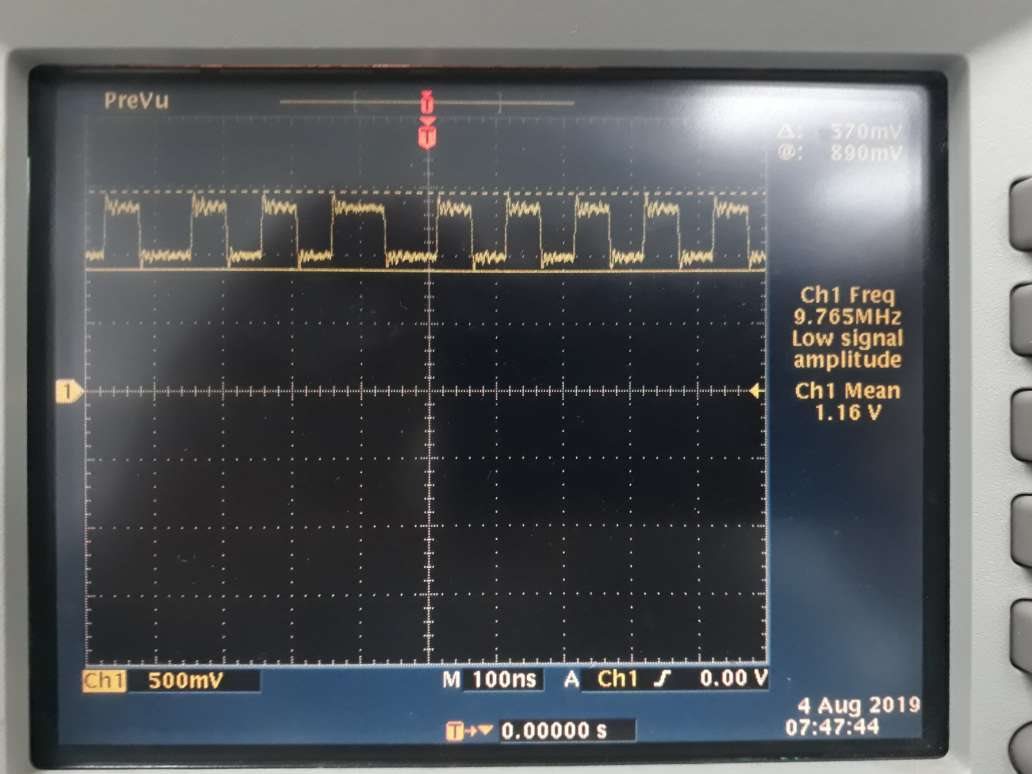

我们使用的是 DS90LV028ATLD/NOPB 器件、输出电平显示的是5V、而不是数据表中提到的3V、任何帮助或建议均请提供。

另一个问题是、我们有5个 Brds、其中一些在 Rout1和 Rou2处显示输出、一些仅在 Rout1、另一些仅在 Rout2处显示输出。

我们测试了2块板、第一块板显示 Out1和 Out2上的输出、第二块板仅显示 Out1

OUT1和 OUT2上的 OUT:5和8之间:5和7之间为3.307V:5和6之间为1.53V (OUT1):1.53V (OUT2)

-仅在 OUT1上输出:5和8之间:5和7之间为3.306V:5和6之间为1.63V (OUT1):2.88V (OUT2)